EP2S60F672C4 FPGA: Χαρακτηριστικά, Εφαρμογές, Προγραμματισμός & Οδηγός Δεδομένων

Σε αυτόν τον οδηγό, θα έχετε μια σαφή επισκόπηση του EP2S60F672C4, ενός ισχυρού FPGA από την οικογένεια Stratix II της Intel.Θα μάθετε για τα κύρια χαρακτηριστικά, την αρχιτεκτονική, τη δομή του μπλοκ και τις τεχνικές προδιαγραφές για να καταλάβετε πώς ταιριάζει σε προηγμένα ψηφιακά σχέδια.Σας περπατά επίσης μέσα από τα βήματα προγραμματισμού, τις εφαρμογές, τα πλεονεκτήματα και τα μειονεκτήματα, ώστε να μπορείτε να δείτε ακριβώς πού και πώς μπορεί να χρησιμοποιηθεί αυτή η συσκευή.Κατάλογος

Ποιο είναι το EP2S60F672C4;

Ο EP2S60F672C4 είναι ένα FPGA υψηλής πυκνότητας από την Intel (πρώην Altera), που ανήκει στην οικογένεια Stratix II.Χτισμένο σε μια διαδικασία SRAM 90 nm, 1,2 V, παρέχει σημαντική λογική χωρητικότητα μέσα σε ένα πακέτο FBGA 672 ball, καθιστώντας το ιδανικό για σύνθετα ψηφιακά συστήματα.Στο πλαίσιο της σειράς EP2S, η συσκευή "60" κάθεται στο εύρος μέσων προς την άνω μέρος της σειράς Stratix II, προσφέροντας ισχυρή ισορροπία λογικής πυκνότητας, ενσωματωμένη μνήμη και πόρους I/O.Γνωστή για την ισχυρή αρχιτεκτονική και την αξιοπιστία του, αυτό το FPGA παραμένει μια αξιόπιστη επιλογή σε πολλά προηγμένα σχέδια.

Ψάχνετε για EP2S60F672C4;Επικοινωνήστε μαζί μας για να ελέγξετε το τρέχον απόθεμα, το χρόνο παράδοσης και την τιμολόγηση.

EP2S60F672C4 CAD μοντέλα

Σύμβολο EP2S60F672C4

EP2S60F672C4 Αποτύπωμα

EP2S60F672C4 3D μοντέλο

Χαρακτηριστικά EP2S60F672C4

• Προχωρημένη διαδικασία 90 nm, 1,2 V CMOS

Το EP2S60F672C4 κατασκευάζεται σε μια διαδικασία CMOS χαλκού 90 nm που εκτελείται σε τάση πυρήνα 1,2 V.Αυτή η τεχνολογία επιτρέπει την υψηλή ταχύτητα, τη μειωμένη κατανάλωση ενέργειας και τη μεγαλύτερη λογική πυκνότητα σε σύγκριση με τις παλαιότερες γενιές FPGA.

• Αρχιτεκτονική Adaptive Logic Module (ALM)

Η συσκευή χρησιμοποιεί ALMS ως λογικό δομικό στοιχείο αντί για παραδοσιακά λογικά στοιχεία.Αυτή η αρχιτεκτονική βελτιώνει τη χρήση των πόρων, επιτρέποντας την αποτελεσματική εφαρμογή των πιο πολύπλοκες λογικές λειτουργίες εντός της ίδιας περιοχής πυριτίου.

• Υψηλή λογική πυκνότητα

Με περίπου 60.440 λογικά στοιχεία (24.176 Alms), το FPGA υποστηρίζει μεγάλα και εξελιγμένα ψηφιακά σχέδια.Αυτή η υψηλή χωρητικότητα το καθιστά κατάλληλο για εφαρμογές όπως η επεξεργασία σήματος, οι επικοινωνίες και τα ενσωματωμένα συστήματα ελέγχου.

• Trimatrix ™ On-Chip Memory

Το EP2S60F672C4 ενσωματώνει τρεις τύπους μπλοκ RAM, (M512, M4K και M-RAM) για να παρέχει συνολικά περίπου 2,4 MBITs ενσωματωμένης μνήμης.Αυτό το μείγμα επιτρέπει την εφαρμογή μικρών FIFOs, μεσαίας αποθήκευσης και μεγάλων αναμνήσεων διπλής θύρας αποτελεσματικά.

• Αφιερωμένα μπλοκ DSP

Η συσκευή περιλαμβάνει 36 αποκλειστικά μπλοκ DSP σχεδιασμένα για αριθμητικές λειτουργίες όπως πολλαπλασιασμούς, συσσωρεύσεις και φιλτράρισμα FIR.Αυτά τα μπλοκ ενισχύουν την απόδοση σε καθήκοντα έντασης υπολογισμού, εξοικονομώντας κατά την εξοικονόμηση γενικών λογικών πόρων.

• Υψηλής ταχύτητας I/O και ακεραιότητα σήματος

Υποστηρίζει διάφορα πρότυπα μονής και διαφορικού I/O μαζί με κύκλωμα δυναμικής ευθυγράμμισης φάσης (DPA).Αυτά τα χαρακτηριστικά επιτρέπουν τη σταθερή μεταφορά δεδομένων υψηλής ταχύτητας έως 1 Gbps, εξασφαλίζοντας αξιόπιστη επικοινωνία με εξωτερικά εξαρτήματα.

• Πλούσια υποστήριξη διεπαφής εξωτερικής μνήμης

Το FPGA είναι συμβατό με DDR, DDR2, QDR II, RLDRAM II και άλλα πρότυπα μνήμης.Η ενσωματωμένη υποστήριξη διεπαφής απλοποιεί το σχεδιασμό του πίνακα και επιτυγχάνει υψηλή απόδοση δεδομένων για εφαρμογές έντασης μνήμης.

• Ευέλικτη διαχείριση ρολογιού

Έως 12 on-chip plls επιτρέπουν τον πολλαπλασιασμό του ρολογιού, τη διαίρεση, τη μετατόπιση φάσης και την εναλλαγή χωρίς σφάλματα.Μπορείτε να τελειοποιήσετε τους τομείς ρολογιών και να μειώσετε το jitter, υποστηρίζοντας τις συχνότητες εσωτερικού ρολογιού έως και 500-550 MHz.

• Κρυπτογράφηση και αναδιάρθρωση bitstream

Το EP2S60F672C4 υποστηρίζει την κρυπτογράφηση Bitstream με βάση την ΑΕ για την εξασφάλιση πνευματικής ιδιοκτησίας.Προσφέρει επίσης απομακρυσμένη ικανότητα αναδιάρθρωσης, επιτρέποντας ενημερώσεις στο πεδίο χωρίς να αντικατασταθούν η συσκευή.

Διάγραμμα μπλοκ Stratix II

Το διάγραμμα μπλοκ Stratix II, όπως φαίνεται για το EP2S60F672C4, απεικονίζει την εσωτερική διάταξη των πόρων της λογικής, της μνήμης και του DSP που αποτελούν τον πυρήνα του FPGA.Τα λογικά μπλοκ συστοιχίας (LABS) είναι διατεταγμένα σε ένα κανονικό πλέγμα, που περιβάλλεται από ενσωματωμένες στήλες RAM και DSP, οι οποίες παρέχουν γρήγορη αριθμητική και δυνατότητες αποθήκευσης on-chip.Τα περιφερειακά στοιχεία I/O και τα δίκτυα ρολογιών πλαισιώνουν αυτή τη δομή, επιτρέποντας την αποτελεσματική μεταφορά δεδομένων και τον έλεγχο χρονισμού μεταξύ του FPGA και των εξωτερικών συσκευών.Αυτό το διάγραμμα είναι σημαντικό επειδή βοηθά στην κατανόηση του τρόπου με τον οποίο τα διαφορετικά λειτουργικά μπλοκ είναι φυσικά οργανωμένα, επιτρέποντάς τους να βελτιστοποιήσουν την τοποθέτηση, τη δρομολόγηση και τη συνολική απόδοση του συστήματος.

Διάγραμμα τραπεζών Stratix II II I/O

Αυτό το διάγραμμα Banks Stratix II I/O Banks απεικονίζει τον τρόπο με τον οποίο οι ακροδέκτες εισόδου/εξόδου του EP2S60F672C4 ομαδοποιούνται και ποια ηλεκτρικά πρότυπα υποστηρίζουν κάθε ομάδα.Κάθε τράπεζα εισόδου/εξόδου έχει σχεδιαστεί για να χειρίζεται συγκεκριμένα επίπεδα τάσης, τύπους σηματοδότησης και λειτουργίες όπως LVTTL, SSTL, LVDS ή πρότυπα εισόδου ρολογιού.Η διάταξη δείχνει πώς διαφορετικές τράπεζες (π.χ., 1, 2, 5, 6 έναντι 3, 4, 7, 8, κλπ.) Βελτιώνονται είτε για εισροές εισόδου/εξόδου γενικής χρήσης είτε για διαφορική σηματοδότηση υψηλής ταχύτητας, συμπεριλαμβανομένης της υποστήριξης για τις εισόδους LVDS/LVPECL στις άκρες.Η κατανόηση αυτής της δομής είναι σημαντική κατά την εκχώρηση ακίδων, επειδή η κατάλληλη επιλογή των τραπεζών εξασφαλίζει ηλεκτρική συμβατότητα, απλοποιεί τη δρομολόγηση του σκάφους και μεγιστοποιεί την απόδοση του FPGA σε σχέδια υψηλής ταχύτητας.

Προδιαγραφές EP2S60F672C4

|

Τύπος |

Παράμετρος |

|

Κατασκευαστής |

Altera/intel |

|

Σειρά |

Stratix® II |

|

Συσκευασία |

Δίσκος |

|

Κατάσταση μέρους |

Απηρχαιωμένος |

|

Αριθμός εργαστηρίων/CLB |

3022 |

|

Αριθμός λογικών στοιχείων/κυττάρων |

60.440 |

|

Συνολικά κομμάτια μνήμης RAM |

2.544,192 |

|

Αριθμός I/O |

492 |

|

Τάση - προμήθεια |

1.15 V ~ 1.25 V |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Θερμοκρασία λειτουργίας |

0 ° C ~ 85 ° C (TJ) |

|

Πακέτο / θήκη |

672-BBGA |

|

Πακέτο συσκευών προμηθευτή |

672-FBGA (27 × 27) |

|

Αριθμός προϊόντος βάσης |

EP2S60 |

Εφαρμογές EP2S60F672C4

1. Επεξεργασία ψηφιακού σήματος (DSP) και φιλτράρισμα

Το EP2S60F672C4 είναι κατάλληλο για την εφαρμογή λειτουργιών DSP υψηλής απόδοσης, όπως φίλτρα FIR και IIR, επεξεργασία FFT και σύνθετες αριθμητικές λειτουργίες.Τα αφιερωμένα μπλοκ DSP χειρίζονται τους πολλαπλασιασμούς και τις συσσωρεύσεις αποτελεσματικά, απελευθερώνοντας γενικούς λογικούς πόρους για άλλες εργασίες.Η μνήμη On-Chip Trimatrix ™ επιτρέπει την ομαλή προσωρινή αποθήκευση δεδομένων και τον αγωγό, το οποίο είναι ιδανικό για επεξεργασία σε πραγματικό χρόνο σε υψηλά ποσοστά δειγματοληψίας.Αυτό καθιστά τη συσκευή ιδανική για εφαρμογές προχωρημένου ήχου, βίντεο και ραντάρ.

2. Επικοινωνία και δικτύωση υψηλής ταχύτητας

Οι διεπαφές I/O υψηλής ταχύτητας της FPGA και οι διασυνδέσεις κυκλώματος I/O της δυναμικής φάσης (DPA) υποστηρίζουν αξιόπιστη μετάδοση δεδομένων Gigabit.Μπορεί να εφαρμόσει πρωτόκολλα επικοινωνίας και λειτουργίες φυσικού στρώματος για συστήματα όπως δρομολογητές, διακόπτες και διασυνδέσεις backplane.Με τη μεγάλη λογική χωρητικότητα και τα ευέλικτα PLL, μπορεί να διαχειρίζεται τις πολύπλοκες μετατροπές χρονισμού και πρωτοκόλλου μεταξύ πολλαπλών διεπαφών υψηλής ταχύτητας.Αυτές οι δυνατότητες το καθιστούν έντονη για την υποδομή τηλεπικοινωνιών και τον εξοπλισμό δικτύωσης υψηλού εύρους ζώνης.

3. Ελεγκτές μνήμης και συστήματα επεξεργασίας δεδομένων

Το EP2S60F672C4 υποστηρίζει διάφορες διεπαφές εξωτερικής μνήμης, συμπεριλαμβανομένων των DDR, DDR2, RLDRAM II και QDR II, καθιστώντας το ιδανικό για το σχεδιασμό ελεγκτών μνήμης υψηλού εύρους ζώνης.Μπορεί να χειριστεί τη ρύθμιση των δεδομένων, τη δημιουργία διευθύνσεων και τη διαιτησία σε υψηλές ταχύτητες με ελάχιστη λανθάνουσα κατάσταση.Ο συνδυασμός δικτύων γρήγορου ρολογιού και ενσωματωμένων μπλοκ RAM επιτρέπει την αποτελεσματική διαχείριση μεγάλων ροών δεδομένων.Αυτό καθιστά το FPGA κατάλληλο για επεξεργασία εικόνας, ροή βίντεο και πλατφόρμες επιστημονικών υπολογιστών που βασίζονται στη διακίνηση βαρέων δεδομένων.

4. Προσαρμοσμένη λογική και ενσωματωμένη επιτάχυνση

Με πάνω από 60.000 λογικά στοιχεία και πλούσια διαχείριση ρολογιών, το FPGA μπορεί να φιλοξενήσει προσαρμοσμένους επιταχυντές υλικού για συγκεκριμένους αλγόριθμους.Οι σχεδιαστές συχνά το χρησιμοποιούν για να εκφορτώσουν υπολογιστικά εντατικά καθήκοντα από CPU, όπως κρυπτογράφηση, ανάλυση πρωτοκόλλου ή βρόχους ελέγχου σε πραγματικό χρόνο.Μπορεί επίσης να ενσωματώσει πολλαπλά λειτουργικά μπλοκ, καθιστώντας το κατάλληλο για σύνθετα σχέδια που μοιάζουν με SOC.Αυτή η ευελιξία το καθιστά πολύτιμο σε εφαρμογές όπως η βιομηχανική αυτοματοποίηση, τα συστήματα ασφαλείας και οι μονάδες ελέγχου της αεροδιαστημικής.

5. Πλατφόρμες πρωτοτύπων και εκπαιδευτικής ανάπτυξης

Η συσκευή EP2S60 βρίσκεται συνήθως σε κιτ ανάπτυξης FPGA που χρησιμοποιούνται για πρωτότυπα, δοκιμές και ακαδημαϊκή έρευνα.Η ισορροπία της λογικής χωρητικότητας, οι δυνατότητες I/O και οι δυνατότητες DSP επιτρέπουν στους μηχανικούς και τους μαθητές να εφαρμόσουν και να επαληθεύουν τα πλήρη συστήματα σε ένα μόνο τσιπ.Υποστηρίζει ταχεία επανάληψη ψηφιακών σχεδίων, επιτρέποντας την επαλήθευση του υλικού πριν από τη δέσμευση στην ανάπτυξη της ASIC.Πολλά πανεπιστήμια και εργαστήρια Ε & Α το χρησιμοποιούν για να διδάξουν τις έννοιες για προηγμένη ψηφιακή σχεδίαση και επεξεργασία σημάτων.

EP2S60F672C4 Παρόμοια μέρη

|

Προσδιορισμός |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Οικογένεια / σειρά |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Λογικά στοιχεία (LE) |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

|

Ελεημοσύνη |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Πακέτο |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Βαθμός ταχύτητας |

C4 (STD) |

C3 (γρηγορότερα) |

C5 (γρηγορότερα) |

C5 (γρηγορότερα) |

I4 (std) |

I3 (γρηγορότερα) |

|

Βαθμός θερμοκρασίας |

Εμπορικό (0 ~ 70 ° C) |

Εμπορικός |

Εμπορικός |

Εμπορικός |

Βιομηχανική (-40 ~ 100 ° C) |

Βιομηχανική (-40 ~ 100 ° C) |

|

I/O καρφίτσες |

492 |

492 |

492 |

492 |

492 |

492 |

|

Μνήμη στο τσιπ |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

|

Τάση πυρήνα |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Βασική διαφορά |

Βασική εμπορική ταχύτητα |

C3 Speed Bin, χωρίς μόλυβδο "n" |

Κάδο υψηλότερης ταχύτητας |

Κάδο υψηλότερης ταχύτητας, παραλλαγή "n" |

Βιομηχανική θερμοκρασία, ίδια πυκνότητα |

Βιομηχανική, ταχύτερη ταχύτητα, χωρίς μόλυβδο |

EP2S60F672C4 Βήματα προγραμματισμού

Πριν μπορέσετε να χρησιμοποιήσετε το EP2S60F672C4 FPGA στο σχέδιό σας, πρέπει να το διαμορφώσετε σωστά με το καταρτισμένο bitstream σας.Αυτή η διαδικασία περιλαμβάνει την προετοιμασία του αρχείου προγραμματισμού, τη ρύθμιση της διασύνδεσης υλικού και τη διασφάλιση ότι η διαμόρφωση φορτώνεται σωστά στην ενεργοποίηση.

Βήμα 1: Δημιουργήστε και συντάξτε το σχέδιό σας

Ξεκινάτε αναπτύσσοντας το λογικό σας σχεδιασμό χρησιμοποιώντας το λογισμικό Intel Quartus II.Μετά την ολοκλήρωση του σχεδιασμού, το συντάξουμε για να δημιουργήσετε το αρχείο προγραμματισμού (.sof ή .pof) ειδικά για τη συσκευή EP2S60F672C4.Οι έλεγχοι της διαδικασίας συλλογής για το χρονισμό, τις αναθέσεις PIN και τη χρήση πόρων για να διασφαλιστεί ότι ο σχεδιασμός σας ταιριάζει μέσα στην αρχιτεκτονική του FPGA.Μόλις καταρτιστεί, το bitstream σας είναι έτοιμο για διαμόρφωση συσκευής.

Βήμα 2: Ρυθμίστε το υλικό προγραμματισμού

Στη συνέχεια, προετοιμάζετε τη διασύνδεση φυσικού προγραμματισμού μεταξύ του υπολογιστή σας και του πίνακα FPGA.Συνήθως, αυτό περιλαμβάνει τη σύνδεση ενός καλωδίου USB-blaster ή συμβατό καλώδιο JTAG στη θύρα JTAG της συσκευής.Θα πρέπει να επαληθεύσετε ότι το Quartus II αναγνωρίζει τον προγραμματιστή και ότι η συσκευή προορισμού ανιχνεύεται σωστά.Αυτό το βήμα εξασφαλίζει σταθερή επικοινωνία πριν ξεκινήσει η διαδικασία διαμόρφωσης.

Βήμα 3: Φορτώστε το αρχείο προγραμματισμού στη συσκευή

Χρησιμοποιώντας το εργαλείο προγραμματιστή Quartus II, προσθέτετε το αρχείο Compiled .SOF OR ή .pof και επιλέξτε το EP2S60F672C4 από τη λίστα εντοπισμένων συσκευών.Στη συνέχεια, ξεκινάτε την ακολουθία προγραμματισμού, κατά τη διάρκεια της οποίας μεταφέρεται και φορτώνεται το bitstream στα κύτταρα διαμόρφωσης SRAM της FPGA.Θα πρέπει να παρακολουθείτε τη γραμμή προόδου και τα μηνύματα κατάστασης για να επιβεβαιώσετε μια επιτυχημένη διαμόρφωση.Μόλις ολοκληρωθεί, το FPGA αρχίζει να εκτελεί αμέσως την προγραμματισμένη λογική.

Βήμα 4: Επαληθεύστε τη διαμόρφωση και τη λειτουργία

Μετά τον προγραμματισμό, επαληθεύετε ότι η συσκευή λειτουργεί όπως προβλέπεται.Το Quartus II παρέχει μια επιλογή επαλήθευσης για να ελέγξετε τη διαμόρφωση CRC και τα σήματα κατάστασης, εξασφαλίζοντας ότι ο σχεδιασμός φορτώνεται σωστά.Μπορείτε επίσης να δοκιμάσετε τις λειτουργίες I/O σας ή να εκτελέσετε μια λειτουργική προσομοίωση για να επιβεβαιώσετε τη συμπεριφορά του συστήματος.Αυτό το τελικό βήμα εξασφαλίζει ότι ο σχεδιασμός σας είναι πλήρως λειτουργικός και σταθερός στο υλικό.

EP2S60F672C4 Πλεονεκτήματα και μειονεκτήματα

Φόντα

• Υψηλή λογική πυκνότητα για σύνθετα σχέδια

• Καλή αναλογία απόδοσης προς κόστος

• Εύκολη μετανάστευση μέσα στην ίδια οικογένεια

• Σταθερά και ώριμα εργαλεία ανάπτυξης

• Αποδεδειγμένη αξιοπιστία στη βιομηχανική χρήση

Μειονεκτήματα

• Παρόπληξη και πιο δύσκολη στην πηγή

• Υψηλότερη κατανάλωση ενέργειας από τα νεότερα FPGAs

• Χωρίς σύγχρονους πομποδέκτες υψηλής ταχύτητας

• πιο δύσκολο κλείσιμο χρονισμού σε υψηλή αξιοποίηση

• Περιορισμένη επεκτασιμότητα για μελλοντικά πρωτόκολλα

EP2S60F672C4 Διαστάσεις συσκευασίας

|

Τύπος |

Παράμετρος |

|

Τύπος πακέτου |

672-FBGA (Fineline BGA) |

|

Μέγεθος σώματος (L × W) |

27,00 mm × 27,00 mm |

|

Συνολικό ύψος πακέτου (α) |

Μέγιστο 3,50 mm |

|

Ύψος standoff (a1) |

Min 0,30 mm |

|

Πάχος υποστρώματος (Α2) |

Μέγιστο 3,00 mm |

|

Διάμετρος μπάλας (β) |

0,50 mm - 0,70 mm |

|

Μπάλα (ε) |

1,00 mm |

|

Αριθμός μπάλες |

672 |

|

Στυλ τοποθέτησης |

Επιφανειακή βάση |

|

Περιγραφή πακέτου |

FBGA, πλέγμα 27 × 27 mm |

EP2S60F672C4 Κατασκευαστής

Το EP2S60F672C4 FPGA κατασκευάζεται από Altera Corporation, ένας κορυφαίος πρωτοπόρος σε προγραμματιζόμενες λογικές συσκευές.Το 2015, η Altera αποκτήθηκε από Πληροφορία, και το προϊόν εμπίπτει τώρα στην ομάδα προγραμματιζόμενων λύσεων της Intel (PSG), η οποία συνεχίζει να υποστηρίζει και να παρέχει τις καθιερωμένες οικογένειες FPGA της Altera.Η Intel διατηρεί τη γραμμή Stratix II ως μέρος του χαρτοφυλακίου προϊόντων της Legacy, εξασφαλίζοντας την τεκμηρίωση, την υποστήριξη εργαλείων και τη μακροπρόθεσμη διαθεσιμότητα για εφαρμογές βιομηχανικών και επικοινωνιών.

Σύναψη

Το EP2S60F672C4 συνδυάζει υψηλή λογική πυκνότητα, ευέλικτη αρχιτεκτονική μνήμης και ισχυρές λειτουργίες I/O για την υποστήριξη σύνθετων ψηφιακών συστημάτων.Η σχεδίαση με βάση το ALM, η μνήμη Trimatrix ™, τα μπλοκ DSP και τα χαρακτηριστικά διαχείρισης ρολογιών επιτρέπουν την αποτελεσματική εφαρμογή των απαιτητικών εφαρμογών.Παρόλο που προσφέρει αποδεδειγμένη αξιοπιστία και ώριμη υποστήριξη ανάπτυξης, αντιμετωπίζει περιορισμούς όπως η απαξίωση και η έλλειψη σύγχρονων πομποδέκτες σε σύγκριση με τις νεότερες γενιές FPGA.Συνολικά, η ισορροπημένη απόδοση και η ευελιξία τους καθιστούν μια σταθερή επιλογή για την επεξεργασία σήματος, την επικοινωνία, τη διαχείριση δεδομένων και τις εφαρμογές πρωτοτύπων.

Φύλλο δεδομένων PDF

EP2S60F672C4 φύλλα δεδομένων:

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Συχνές ερωτήσεις [FAQ]

1 Μπορεί το EP2S60F672C4 να συνεργαστεί με τις σύγχρονες διεπαφές μνήμης DDR;

Ναι, υποστηρίζει διεπαφές DDR, DDR2, QDR II και RLDRAM II, οι οποίες καλύπτουν πολλά κοινά πρότυπα εξωτερικής μνήμης.Αυτό το καθιστά κατάλληλο για εφαρμογές επεξεργασίας δεδομένων υψηλού εύρους ζώνης.

2. Το EP2S60F672C4 απαιτεί ειδικό χειρισμό ή αποθήκευση;

Ναι, όπως και άλλα συστατικά που έχουν συσκευαστεί από την BGA, θα πρέπει να αποθηκεύονται σε συσκευασία ελεγχόμενες με υγρασία και να χειρίζονται με προστασία ESD.Ακολουθώντας τις κατάλληλες πρακτικές αποθήκευσης βοηθά στη διατήρηση της δυνατότητας συγκόλλησης και της αξιοπιστίας των συσκευών κατά τη διάρκεια της συναρμολόγησης.

3. Πώς μπορείτε να μειώσετε την κατανάλωση ενέργειας σε σχέδια EP2S60F672C4;

Μπορείτε να βελτιστοποιήσετε τη χρήση λογικής, τα αχρησιμοποίητα ρολόγια της πύλης, τις χαμηλότερες τάσεις εισόδου/εξόδου όπου είναι δυνατόν και να αξιοποιήσετε τις επιλογές σύνθεσης ισχύος στο Quartus II για να ελαχιστοποιήσετε τη συνολική κλήρωση ισχύος.

4. Ποια εργαλεία προγραμματισμού απαιτούνται για το EP2S60F672C4;

Θα χρειαστείτε λογισμικό Intel Quartus II για σχεδιασμό, συλλογή και προγραμματισμό, μαζί με ένα USB-Blaster ή συμβατό καλώδιο JTAG για να διαμορφώσετε τη συσκευή.

5. Το EP2S60F672C4 υποστηρίζει ενημερώσεις στο πεδίο ή απομακρυσμένη αναδιάρθρωση;

Ναι, υποστηρίζει την κρυπτογράφηση Bitstream με βάση το AES και την απομακρυσμένη αναδιάρθρωση, επιτρέποντάς σας να ενημερώσετε με ασφάλεια το σύστημά σας χωρίς να αντικαταστήσετε φυσικά το FPGA.

Τα πάντα για το LFXP6C-3FN256C Lattice Semiconductor

στο 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, Χαρακτηριστικά, Προγραμματισμός και Οδηγός φύλλου δεδομένων

στο 2025/10/3

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/18 147778

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/18 112035

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/18 111352

-

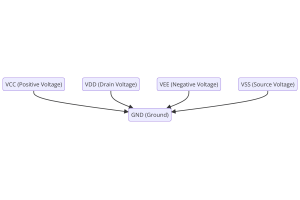

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/18 83792

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79602

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66976

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63111

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63044

-

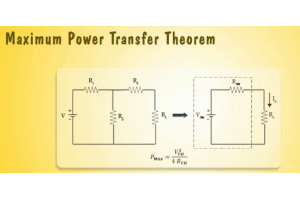

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54097

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52198