ΣπίτιBlogSR Flip-Flop Οδηγός Γνώσης-Αρχή Εργασίας, Πλεονεκτήματα, Μειονεκτήματα, Πίνακας Αλήθειας και Διαφορές από το RS Flip-Flop

SR Flip-Flop Οδηγός Γνώσης-Αρχή Εργασίας, Πλεονεκτήματα, Μειονεκτήματα, Πίνακας Αλήθειας και Διαφορές από το RS Flip-Flop

Το Flip-Flop είναι απλώς ένας όρος που αναφέρεται σε μια ψηφιακή ηλεκτρονική συσκευή, η οποία είναι ένα ηλεκτρονικό στοιχείο που χρησιμοποιείται για την αποθήκευση ενός μόνο κομμάτι πληροφοριών.

Το SR Flip-Flop (flip-flop set-reset) είναι ένα βασικό συστατικό των ψηφιακών ηλεκτρονικών κυκλωμάτων που χρησιμοποιούνται για την αποθήκευση και χειρισμό δεδομένων.Λειτουργεί με διαδοχικό τρόπο.Τα SR Flip-Flops μπορούν να κατασκευαστούν χρησιμοποιώντας μάνδαλα SR.Ένα μάνδαλο είναι ένα ψηφιακό ηλεκτρονικό κύκλωμα που παίρνει την απλή μορφή ενός στοιχείου αποθήκευσης, ικανό να αποθηκεύει ένα κομμάτι δυαδικών πληροφοριών (0 ή 1).Σε αυτό το άρθρο, θα συζητήσουμε το SR Flip-Flop, συμπεριλαμβανομένης της αρχής λειτουργίας, του πίνακα αλήθειας, των πλεονεκτημάτων, των μειονεκτήματα και των διαφορών από το RS Flip-Flop.

Κατάλογος

1. Αρχή λειτουργίας SR Flip-Flop

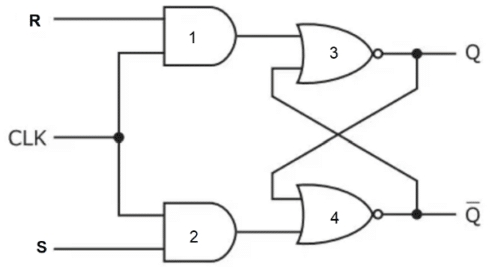

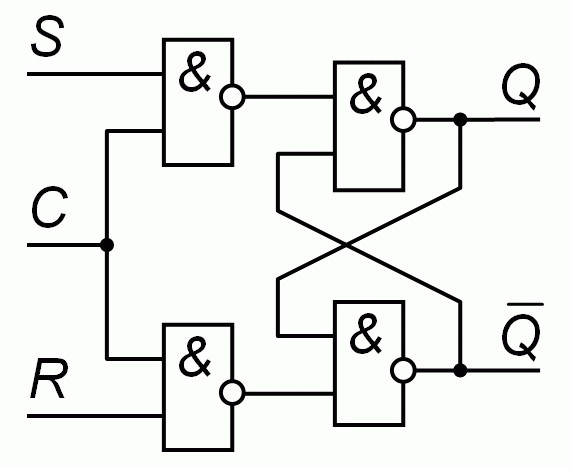

Το απλούστερο RS flip-flop μπορεί να κατασκευαστεί χρησιμοποιώντας δύο 2 εισόδους ή πύλες, όπως φαίνεται στο διάγραμμα:

Λάβετε υπόψη ότι ο τρόπος με τον οποίο συνδέονται τα στοιχεία διασφαλίζει ότι βρίσκονται πάντα σε αντίθετα κράτη.Εάν η έξοδος του πρώτου στοιχείου είναι 1, τότε η έξοδος του δεύτερου στοιχείου θα είναι 0 και αντίστροφα.

Για ευκολία κατανόησης, εδώ είναι τα τέσσερα σενάρια που μπορεί να συμβούν με ένα SR flip-flop:

Σενάριο 1: S = 0, r = 0

Έξοδος πύλης: Τόσο το GATE1 όσο και το GATE2 εξόδου 0. Κατάσταση συντήρησης: Δεδομένου ότι οι πύλες 3 και 4 είναι ούτε πύλες, με μία είσοδο στο 0, οι εξόδους τους εξαρτώνται από τη δεύτερη είσοδο.Έτσι, το GATE3/Q (N+1) διατηρεί την προηγούμενη κατάσταση Q και το GATE4/Q (N+1) διατηρεί την συμπληρωματική κατάσταση Q ".

Σενάριο 2: S = 0, r = 1

Έξοδος πύλης: Έξοδος GATE1 1 (δεδομένου ότι το R είναι υψηλό), η έξοδος GATE2 0. Επαναφορά λειτουργίας: Για το GATE3, η μία είσοδος είναι υψηλή (από την GATE1), οδηγώντας σε έξοδο 0 μέσω της λειτουργίας NOR, επαναφέροντας έτσι την κατάσταση.Ωστόσο, μία είσοδος στο GATE4 παραμένει χαμηλή, παραγωγή 1, υποδεικνύοντας την συμπληρωματική κατάσταση.

Σενάριο 3: S = 1, r = 0

Έξοδος πύλης: Έξοδοι GATE1 0, GATE2 Έξοδοι 1 (δεδομένου ότι το S είναι υψηλό).Λειτουργία SET: Αυτή τη στιγμή, το GATE3 εξάγει 1 (η άλλη είσοδος από το GATE1 είναι χαμηλή), ρυθμίζοντας το flip-flop.Αντίθετα, λόγω της υψηλής εισόδου από το GATE2, το GATE4 εξάγει 0, επιβεβαιώνοντας την συμπληρωματική κατάσταση.

Σενάριο 4: S = 1, r = 1

Έξοδος πύλης: Με τις δύο εισόδους υψηλές, και οι δύο πύλες εξόδου 1. Μη έγκυρη κατάσταση: Όταν και οι δύο εισόδους είναι υψηλές, οι πύλες 3 και 4 και οι δύο εξόδου 0, με αποτέλεσμα μια σύγκρουση επειδή πρέπει ναΝα είστε συμπληρωματικά αποτελέσματα, αλλά αυτό δεν συμβαίνει, οδηγώντας σε αυτό το κράτος να είναι άκυρο.

2. Πίνακας αλήθειας SR Flip-Flop

|

μικρό |

R |

Ε (N+1) |

Κατάσταση |

|

0 |

0 |

ΕΝ |

Χωρίς αλλαγή |

|

0 |

1 |

0 |

ΕΠΑΝΑΦΟΡΑ |

|

1 |

0 |

1 |

ΣΕΙΡΑ |

|

1 |

1 |

X |

ΑΚΥΡΟΣ |

Θα χρησιμοποιήσουμε αυτόν τον πίνακα αλήθειας για να γράψουμε τον χαρακτηριστικό πίνακα για το Flip-Flop SR.Στον πίνακα αλήθειας, μπορείτε να δείτε δύο εισόδους, S και R, και μία έξοδο, Q (N+1).Ωστόσο, στον χαρακτηριστικό πίνακα, θα δείτε τρεις εισόδους, S, R, και QN, και μία έξοδο, Q (N+1).

Από το λογικό διάγραμμα, είναι σαφές ότι τα QN και QN 'είναι δύο συμπληρωματικές εξόδους, που λειτουργούν επίσης ως εισροές στις πύλες 3 και 4, οπότε θεωρούμε το QN, την τρέχουσα κατάσταση του flip-flop, ως είσοδο και Q (n (n+1), η επόμενη κατάσταση, ως έξοδος.

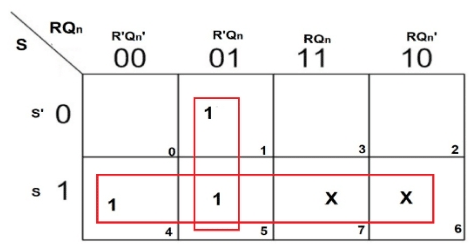

Αφού γράψουμε τον χαρακτηριστικό πίνακα, θα σχεδιάσουμε έναν 3-μεταβλητό K-MAP για να αντλήσουμε τη χαρακτηριστική εξίσωση.

3. Χαρακτηριστικός πίνακας

|

μικρό |

R |

ΕΝ |

Ε (N+1) |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

X |

|

1 |

1 |

1 |

X |

Από το K-MAP, παίρνετε δύο ζευγάρια.Μετά την επίλυση και των δύο, λαμβάνουμε την ακόλουθη χαρακτηριστική εξίσωση:

Q (n + 1) = s + r'qn

4. Πλεονεκτήματα του SR flip-flop

Η χρήση του SR flip-flops έχει πολλά πλεονεκτήματα.Παρακάτω είναι μερικά από αυτά:

- Απλότητα: Ο σχεδιασμός του SR flip-flops είναι σχετικά απλός, που αποτελείται μόνο από λίγες πύλες.Μπορούν εύκολα να ενσωματωθούν σε μεγαλύτερα κυκλώματα χωρίς να περιπλέκουν το συνολικό σχεδιασμό.

- Ταχύτητα: Τα Flip-Flops SR λειτουργούν με υψηλή ταχύτητα.Μπορούν να αλλάξουν γρήγορα μεταξύ των καταστάσεων ρύθμισης και επαναφοράς χωρίς καθυστέρηση, εξασφαλίζοντας ότι τα ψηφιακά συστήματα μπορούν να εκτελούν πιο αποτελεσματικά εργασίες, βελτιώνοντας έτσι την απόδοση των τεχνολογιών που βασίζονται στην ταχεία επεξεργασία δεδομένων.

- Χαμηλή κατανάλωση ενέργειας: Τα Flip-Flops SR καταναλώνουν πολύ λίγη ισχύ, καθιστώντας τα ιδανικά για χρήση σε συσκευές με μπαταρία, όπως κινητά τηλέφωνα και φορητές υπολογιστικές συσκευές, ενώ δίνουν επίσης χαμηλότερο λειτουργικό κόστος όσον αφορά τη χρήση ενέργειας.

- Λειτουργία Bistable: Το SR flip-flops μπορεί να διατηρήσει επ 'αόριστον μια κατάσταση (σετ ή επαναφορά) μέχρις ότου ένα σήμα εισόδου προτρέψει μια αλλαγή και η δυνατότητα διατήρησης μιας σταθερής κατάστασης χωρίς σταθερή είσοδο καθιστά τα SR flip-flops χρήσιμα για διάφορες εφαρμογές.

5. Περιορισμοί του SR flip-flops

Παρά τα πολλά πλεονεκτήματα, τα Flip-Flops SR έχουν επίσης ορισμένους περιορισμούς.Παρακάτω είναι μερικά από αυτά:

- Συνθήκες φυλής: Τα Flip-Flops SR είναι ευαίσθητα σε συνθήκες φυλής όπου η κατάσταση εξόδου μπορεί να αλλάξει απρόβλεπτα λόγω αλλαγών στο χρονοδιάγραμμα των σημάτων εισόδου, ενδεχομένως να οδηγεί σε σφάλματα ή απροσδόκητα αποτελέσματα.

- Μη έγκυρη κατάσταση: Ένας εγγενής περιορισμός των flip-flops SR είναι η συμπεριφορά τους όταν και οι δύο εισόδους (S) και επαναφοράς (R) είναι ενεργές ταυτόχρονα.Σε αυτή την περίπτωση, το flip-flop εισέρχεται σε μια άκυρη κατάσταση, συχνά με αποτέλεσμα και οι δύο εξόδους να είναι υψηλές ή χαμηλές, γεγονός που παραβιάζει τη βασική αρχή λειτουργίας μιας διστακτικής συσκευής.Αυτή η άκυρη κατάσταση μπορεί να διαταράξει την κανονική λειτουργία των ψηφιακών κυκλωμάτων, οδηγώντας σε απρόβλεπτη συμπεριφορά του συστήματος και πιθανή απώλεια δεδομένων.

- Περιορισμένη επεκτασιμότητα: Το SR flip-flops μπορεί να είναι δύσκολο να κλιμακωθεί σε πιο σύνθετα ψηφιακά συστήματα καθώς η πολυπλοκότητα του συστήματος αυξάνεται, η πιθανότητα εισαγωγής σφαλμάτων λόγω της βασικής φύσης των flip-flops SR.

6. Περιοχές εφαρμογής

- Συστήματα ελέγχου: Στα συστήματα ελέγχου, τα Flip-Flops SR μπορούν να επιτύχουν ομαλές μεταβάσεις μεταξύ των σημάτων, ελαχιστοποιώντας έτσι τους κινδύνους ατυχημάτων και τη βελτίωση της ροής της κυκλοφορίας.Μια κοινή εφαρμογή είναι στα συστήματα ελέγχου φωτός της κυκλοφορίας, όπου τα Flip-Flops SR συμβάλλουν στη διαχείριση της ακολουθίας των φανών της κυκλοφορίας, εξασφαλίζοντας ότι τα σήματα αλλάζουν με ακριβή και ομαλή τρόπο, με τον τρόπο αυτό με ασφάλεια και αποτελεσματικά τον έλεγχο της ροής της κυκλοφορίας.

- Αποθήκευση μνήμης: Τα Flip-Flops SR είναι επίσης θεμελιώδη συστατικά των συσκευών αποθήκευσης μνήμης, όπως τα μητρώα.Χρησιμοποιούνται για την προσωρινή αποθήκευση δεδομένων σε υπολογιστικές συσκευές που κυμαίνονται από μικροεπεξεργαστές έως ψηφιακούς επεξεργαστές σήματος, επιτρέποντας γρήγορη πρόσβαση και χειρισμό δεδομένων κατά τη διάρκεια των εργασιών επεξεργασίας.

- Ψηφιακοί μετρητές: Τα Flip-Flops SR χρησιμοποιούνται σε ψηφιακούς μετρητές για λειτουργίες μέτρησης, επιτρέποντας την αύξηση ή τη μείωση με βάση τα σήματα εισόδου.

- Συγχρονισμός δεδομένων: Τα Flip-Flops SR είναι ζωτικής σημασίας για τον συγχρονισμό των σημάτων δεδομένων μεταξύ δύο ψηφιακών κυκλωμάτων, εξασφαλίζοντας ότι λειτουργούν ταυτόχρονα στον ίδιο κύκλο ρολογιού, ο οποίος είναι πολύ χρήσιμος για τη διατήρηση της αξιοπιστίας των δικτύων επικοινωνίας.

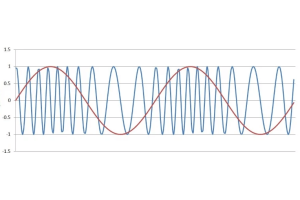

- Οι ταλαντωτές: Όταν συνδυάζονται με άλλα εξαρτήματα, τα flip-flops SR μπορούν να σχηματίσουν απλούς ταλαντωτές που παράγουν περιοδικά σήματα.Αυτό είναι ιδιαίτερα χρήσιμο σε εφαρμογές όπως τα κυκλώματα ρολογιού και οι γεννήτριες ήχου σήματος όπου απαιτείται συνεπής και σταθερή παραγωγή σήματος.

7. Διαφορές μεταξύ SR και RS flip-flops

|

Χαρακτηριστικό |

Sr flip-flop |

Rs flip-flop |

|

S = 0, r = 0 |

Q Κατάσταση (καμία αλλαγή) διατηρήθηκε. |

Q Κατάσταση (καμία αλλαγή) διατηρήθηκε. |

|

S = 0, r = 1 |

Επαναφορά (Q = 0) |

Επαναφορά (Q = 0) |

|

S = 1, r = 0 |

Set (q = 1) |

Set (q = 1) |

|

S = 1, r = 1 |

Set (κυρίαρχο) (q = 1) |

Επαναφορά (κυρίαρχη) (Q = 0) |

|

Φόντα: |

Όταν τα S και R είναι και τα δύο, η λειτουργία καθορισμού

έχει προτεραιότητα. |

Όταν τα S και R είναι και τα δύο, η λειτουργία επαναφοράς

έχει προτεραιότητα. |

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

→ Προηγούμενος

Συχνά παραβλέπονται αλλά εξαιρετικά σημαντικές, οι μπαταρίες AG1 ενεργοποιούν μια ποικιλία συσκευών από καθημερινά gadgets σε ιατρικό εξοπλισμό.Οι μπαταρίες AG1, διαθέσ...

Η κατανόηση της χωρητικότητας της μπαταρίας του αυτοκινήτου σας και του τρόπου με τον οποίο εκτελεί κάτω από διάφορες συνθήκες είναι σημαντική για κάθε ιδιοκτήτη ...

→ επόμενος

Ag1 ισοδύναμες αντικαταστάσεις μπαταρίας

στο 2024/04/27

Πόσο γνωρίζετε για το CCA;

στο 2024/04/26

Δημοφιλείς θέσεις

-

Τι είναι το GND στο κύκλωμα;

στο 1970/01/1 2937

-

Οδηγός σύνδεσης RJ-45: Κωδικοί σύνδεσης RJ-45, Σχέδια καλωδίωσης, Εφαρμογές R-J45, RJ-45 Datasheets

στο 1970/01/1 2501

-

Τύποι σύνδεσης ινών: SC vs LC και LC VS MTP

στο 1970/01/1 2089

-

Κατανόηση τάσεων τροφοδοσίας σε ηλεκτρονικά VCC, VDD, VEE, VSS και GND

στο 0400/11/9 1893

-

Σύγκριση μεταξύ DB9 και RS232

στο 1970/01/1 1763

-

Τι είναι η μπαταρία LR44;

Η ηλεκτρική ενέργεια, αυτή η πανταχού παρούσα δύναμη, διαπερνά ήσυχα κάθε πτυχή της καθημερινής μας ζωής, από τα ασήμαντα gadgets έως τον απειλητικό για τη ζωή ιατρική εξοπλισμό, παίζει έναν σιωπηλό ρόλο.Ωστόσο, η πραγματικ...στο 1970/01/1 1713

-

Κατανόηση των θεμελιωδών στοιχείων: Αντίσταση επαγωγής, και καταφύγιο

Στον περίπλοκο χορό της Ηλεκτρολόγων Μηχανικών, ένα τρίο θεμελιωδών στοιχείων παίρνει το κεντρικό στάδιο: επαγωγή, αντίσταση και χωρητικότητα.Κάθε φέρει μοναδικά χαρακτηριστικά που υπαγορεύουν τους δυναμικούς ρυθμο...στο 1970/01/1 1655

-

CR2430 Περιεκτικός οδηγός μπαταρίας: Προδιαγραφές, εφαρμογές και σύγκριση με μπαταρίες CR2032

Τι είναι η μπαταρία CR2430;Οφέλη από μπαταρίες CR2430ΚανόναςΕφαρμογές μπαταρίας CR2430CR2430 ισοδύναμοCR2430 VS CR2032Μέγεθος μπαταρίας CR2430Τι να ψάξετε όταν αγοράζετε το CR2430 και τα ισοδύναμαΦύλλο δεδομένων PDFΣυχνές ερωτήσεις Οι μπαταρ...στο 1970/01/1 1553

-

Τι είναι το RF και γιατί το χρησιμοποιούμε;

Η τεχνολογία ραδιοσυχνότητας (RF) αποτελεί βασικό μέρος της σύγχρονης ασύρματης επικοινωνίας, επιτρέποντας τη μετάδοση δεδομένων σε μεγάλες αποστάσεις χωρίς φυσικές συνδέσεις.Αυτό το άρθρο βυθίζεται στα βασικά του RF, ...στο 1970/01/1 1539

-

CR2450 VS CR2032: Μπορεί να χρησιμοποιηθεί η μπαταρία;

Οι μπαταρίες του μαγγανίου λιθίου έχουν κάποιες ομοιότητες με άλλες μπαταρίες λιθίου.Η υψηλή ενεργειακή πυκνότητα και η μακρά διάρκεια ζωής είναι τα χαρακτηριστικά που έχουν κοινό.Αυτό το είδος μπαταρίας έχει κερδίσε...στο 1970/01/1 1512