XCV200-6FG456C FPGA: Χαρακτηριστικά, προδιαγραφές, προγραμματισμός και εφαρμογές

Το XCV200-6FG456C είναι ένα ισχυρό FPGA (συστοιχία πύλης προγραμματιζόμενης πεδίου) από τη σειρά AMD Xilinx Virtex®.Αυτός ο οδηγός εξηγεί τα χαρακτηριστικά του, τη διάταξη PIN, τα βήματα προγραμματισμού και τις χρήσεις.Με υψηλή ισχύ επεξεργασίας, ευέλικτες επιλογές σχεδιασμού και ισχυρές δυνατότητες εισόδου/εξόδου (I/O), αυτό το FPGA βοηθά στην οικοδόμηση γρήγορων και αξιόπιστων ψηφιακών συστημάτων.Είτε εργάζεστε σε δικτύωση, συστήματα ελέγχου ή Custom Electronics, αυτός ο οδηγός θα σας βοηθήσει να καταλάβετε πώς μπορεί να χρησιμοποιηθεί στα έργα σας το XCV200-6FG456C στα έργα σας.Κατάλογος

Επισκόπηση XCV200-6FG456C

Ο XCV200-6FG456C είναι ένα αξιοσημείωτο μοντέλο εντός της οικογένειας AMD Xilinx Virtex® FPGA, που έχει σχεδιαστεί για να παρέχει ισχυρές προγραμματιζόμενες λύσεις λογικής για σύνθετα ψηφιακά συστήματα.Αυτό το συγκεκριμένο τσιπ περιλαμβάνει περίπου 236.666 πύλες συστήματος και διαθέτει 1.176 διαμορφώσιμα λογικά μπλοκ (CLBS) και 5.292 λογικά κύτταρα.Περιλαμβάνει επίσης 57.344 συνολικά κομμάτια μνήμης RAM και υποστηρίζει 284 ακίδες I/O, που στεγάζονται σε ένα πακέτο πλέγματος πλέγματος πλέγματος (FBGA) 456-μπάλας (FBGA), μετρώντας 23mm x 23mm.Αυτό το μοντέλο λειτουργεί σε ονομαστική τάση 2.5V, με εύρος 2.375V έως 2.625V, και μπορεί να λειτουργήσει σε κλίμακα θερμοκρασίας από 0 ° C έως 85 ° C.Η ευρύτερη σειρά Virtex® εξυπηρετεί μια σειρά εφαρμογών με πυκνότητες από 50.000 έως πάνω από 1 εκατομμύριο πύλες συστήματος και ρυθμούς ρολογιού συστήματος μέχρι 200 MHz.Υποστηρίζει πολυάριθμα πρότυπα I/O, όπως LVTTL, LVCMOS και PCI, μεταξύ άλλων.Χαρακτηριστικά όπως βρόχοι με καθυστέρηση (DLL), διαμορφώσιμα λογικά μπλοκ με ενσωματωμένη μνήμη και αφοσιωμένη λογική μεταφοράς για αριθμητικές λειτουργίες ενισχύουν τη λειτουργικότητά της.Κατασκευασμένη με τη χρήση μεταλλικής διαδικασίας μέταλλο 0,22 μm 5 στρώσεων, η οικογένεια Virtex® εγγυάται την απόδοση και την αξιοπιστία.

Αν ψάχνετε να ενσωματώσετε την τεχνολογία FPGA κορυφαίου επιπέδου στα προϊόντα ή τα συστήματά σας, η αγορά του XCV200-6FG456C χύμα μαζί μας είναι μια έξυπνη κίνηση.Αντιμετωπίζει τα πρότυπα της βιομηχανίας και σας κρατά μπροστά από τις μελλοντικές τεχνολογικές ανάγκες.

Χαρακτηριστικά XCV200-6FG456C

• Πύλες συστήματος: Το XCV200-6FG456C προσφέρει περίπου 236.666 πύλες συστήματος.Αυτός ο υψηλός αριθμός πύλης επιτρέπει την εφαρμογή σύνθετων ολοκληρωμένων κυκλωμάτων ψηφιακής λογικής σε ένα μόνο τσιπ, ενισχύοντας τόσο την απόδοση όσο και την ευελιξία σε μια σειρά εφαρμογών.

• Λογικοί πόροι: Περιλαμβάνει 1.176 διαμορφώσιμα λογικά μπλοκ (CLBS) και 5.292 λογικά κύτταρα.Αυτοί οι πόροι είναι καλοί για το σχεδιασμό ευέλικτων και κλιμακωτών ψηφιακών κυκλωμάτων.Τα CLBs μπορούν να προγραμματιστούν για να εκτελέσουν μια μεγάλη ποικιλία λογικών λειτουργιών, ενώ ο μεγάλος αριθμός λογικών κυττάρων επιτρέπει τη διαχείριση εκτεταμένων λειτουργιών και διαδικασιών λογικής.

• Μνήμη: Η συσκευή παρέχει 57.344 κομμάτια μνήμης RAM, που διανέμονται μεταξύ των λογικών της μπλοκ.Αυτή η ενσωματωμένη μνήμη RAM χρησιμοποιείται για εφαρμογές που απαιτούν γρήγορη και αποτελεσματική αποθήκευση και ανάκτηση δεδομένων, υποστηρίζοντας λειτουργίες δεδομένων υψηλής ταχύτητας που είναι αναπόσπαστο μέρος των σύγχρονων ψηφιακών συστημάτων.

• Δυνατότητες εισόδου/εξόδου: Με 284 ακροδέκτες εισόδου/εξόδου, οι XCV200-6FG456C διευκολύνουν τις εκτεταμένες δυνατότητες διασύνδεσης.Αυτές οι ακίδες εισόδου/εξόδου υποστηρίζουν διάφορα πρότυπα σημάτων και επιτρέπουν στο FPGA να επικοινωνεί αποτελεσματικά με άλλα συστατικά σε ένα σύστημα, όπως συσκευές μνήμης, επεξεργαστές και περιφερειακά.

• Εύρος τάσης και θερμοκρασίας: Λειτουργώντας σε ονομαστική τάση 2,5V, με αποδεκτό εύρος από 2,375V έως 2,625V, αυτό το FPGA έχει σχεδιαστεί για κατανάλωση χαμηλής ισχύος διατηρώντας παράλληλα ισχυρή απόδοση.Μπορεί να λειτουργήσει σε εύρος θερμοκρασίας διασταύρωσης 0 ° C έως 85 ° C, εξασφαλίζοντας αξιοπιστία υπό ποικίλες περιβαλλοντικές συνθήκες.

XCV200-6FG456C Διάγραμμα λειτουργίας PIN

Ο XCV200-6FG456C Διάγραμμα λειτουργίας PIN είναι μια δομημένη αναπαράσταση των αναθέσεων PIN της FPGA, κατηγοριοποιημένες σε διαφορετικές τράπεζες (Τράπεζα 0 έως Τράπεζα 7).Κάθε τράπεζα ομάδων καρφίτσες με βάση τη λειτουργία και τη φυσική τοποθέτηση στο πακέτο FPGA.Το σύστημα αρίθμησης και επισήμανσης ακολουθεί ένα μοτίβο πλέγματος όπου οι σειρές υποδηλώνονται με γράμματα (A, B, C, κλπ.) Και οι στήλες ανά αριθμό (1, 2, 3, κλπ.), Γεγονός που διευκολύνει την ταχεία ταυτοποίηση συγκεκριμένων ακίδων.Αυτές οι τράπεζες αντιστοιχούν σε διαφορετικές λειτουργίες εισόδου/εξόδου, ισχύ, γείωση και ειδική δρομολόγηση σήματος.Οι ακίδες αποδίδονται σε διάφορες λειτουργικές ομάδες, συμπεριλαμβανομένων των I/O (GPIO) γενικών χρήσεων, που συχνά χαρακτηρίζονται ως "G" (γενική είσοδος/έξοδος), "V" (παροχή τάσης) και "O" (έξοδος).Οι καρφίτσες ισχύος και γείωσης σημειώνονται σαφώς, εξασφαλίζοντας σταθερή λειτουργία FPGA.Οι καρφίτσες ειδικού σκοπού, όπως εισόδους ρολογιού, επαναφορές και σήματα ελέγχου, αναγνωρίζονται με σύμβολα όπως "R" ή "T."Ορισμένες καρφίτσες εξυπηρετούν επίσης αφοσιωμένους ρόλους επικοινωνίας, συμπεριλαμβανομένης της διαμόρφωσης JTAG και της χρονομέτρησης υψηλής ταχύτητας, για προγραμματισμό και εντοπισμό σφαλμάτων.

Xcv200-6fg456c Διάγραμμα μπλοκ

Μπλοκ εισόδου/εξόδου

Το διάγραμμα αντιπροσωπεύει το Μπλοκ εισόδου/εξόδου (IOB) Δομή του XCV200-6FG456C FPGA, το οποίο είναι μέλος της οικογένειας Xilinx Virtex.Το διάγραμμα παρουσιάζει βασικά στοιχεία που εμπλέκονται στις λειτουργίες εισόδου και εξόδου, επισημαίνοντας τους μηχανισμούς ροής και ελέγχου δεδομένων.Στον πυρήνα του διαγράμματος, χρησιμοποιούνται τρία flip-flops για την καταχώριση σημάτων για την είσοδο, την έξοδο και τον έλεγχο τριών κρατών.Ο καταχωρητής εξόδου ελέγχεται από το σήμα OCE (Enable Enable Enable), το οποίο καθορίζει πότε τα δεδομένα εξόδου είναι συνδεδεμένα.Ομοίως, ο μητρώος τριών κρατών ελέγχεται από το TCE (Enable Clock Enable), επιτρέποντας ή απενεργοποιώντας το buffer εξόδου.Ο καταχωρητής εισόδου καταγράφει τα εισερχόμενα δεδομένα και εφαρμόζει προγραμματιζόμενη καθυστέρηση πριν την περάσει στην εσωτερική λογική FPGA μέσω του IBUF (buffer εισόδου).Το obuft (buffer εξόδου Tri-State) εξασφαλίζει ότι το FPGA μπορεί είτε να οδηγήσει ένα σήμα πάνω στο PAD (PIN I/O) είτε να το τοποθετήσει σε κατάσταση υψηλής έντασης, ανάλογα με τη λογική ελέγχου.Ένα αδύναμο κύκλωμα φύλαξης περιλαμβάνεται στο μαξιλάρι για να διατηρηθεί η τελευταία γνωστή λογική κατάσταση όταν δεν υπάρχει ενεργός οδηγός, αποτρέποντας τις ακούσιες επιπτώσεις.Η τάση αναφοράς (VREF) χρησιμοποιείται για ορισμένα πρότυπα εισόδου, όπως SSTL ή HSTL, τα οποία απαιτούν ακριβή επίπεδα τάσης για σωστή λειτουργία.Συνολικά, αυτή η δομή IOB επιτρέπει στο FPGA να διαχειρίζεται τη μετάδοση δεδομένων υψηλής ταχύτητας, να υποστηρίζει διαφορετικά πρότυπα I/O και να παρέχει ευέλικτο έλεγχο του χρονισμού και της ακεραιότητας του σήματος.

Master/Slave Serial Mode

Ο Master/Slave Serial Mode Το μπλοκ διάγραμμα απεικονίζει τη διαδικασία διαμόρφωσης ενός FPGA Virtex, συγκεκριμένα του XCV200-6FG456C, όταν προγραμματίζεται σε διαμόρφωση Daisy-Chain χρησιμοποιώντας ένα σειριακό EEPROM (XC1701L).Σε αυτή τη ρύθμιση, μια συσκευή Virtex λειτουργεί ως κύριος, ελέγχει το ρολόι διαμόρφωσης (CCLK) και μεταδίδει σειριακά δεδομένα διαμόρφωσης σε επιπλέον FPGAs στην αλυσίδα.Το κύριο FPGA ξεκινά τη διαδικασία διαμόρφωσης επιβεβαιώνοντας το σήμα του προγράμματος, επαναφέροντας όλες τις συσκευές στην αλυσίδα.Μόλις ολοκληρωθεί η αρχικοποίηση, το σήμα INIT υποδεικνύει την ετοιμότητα και οι ροές δεδομένων διαμόρφωσης από το σειριακό EEPROM (XC1701L) στον ακροδέκτη DIN (δεδομένων) του κύριου FPGA.Το Master FPGA διαβάζει δεδομένα από το EEPROM και το προωθεί μέσω του DOUT (Data Out) σε επακόλουθα FPGAs Slave, συγχρονίζοντας τη μεταφορά δεδομένων χρησιμοποιώντας το σήμα CCLK.Το σήμα που ολοκληρώθηκε χρησιμοποιείται για να υποδείξει επιτυχή διαμόρφωση, με μια προαιρετική αντίσταση pull-up που εξασφαλίζει μια σταθερή υψηλή κατάσταση όταν ολοκληρωθεί η διαμόρφωση.Το XC1701L EEPROM ελέγχεται από το κύριο FPGA χρησιμοποιώντας CLK, δεδομένα, CE (chip enable) και επαναφέρονται σήματα/OE (enable enable), εξασφαλίζοντας ότι τα αποθηκευμένα δεδομένα διαμόρφωσης ανακτώνται σωστά.Αυτή η μέθοδος διαμόρφωσης είναι αποτελεσματική για τον προγραμματισμό πολλαπλών FPGA χρησιμοποιώντας ένα μόνο EEPROM, μειώνοντας την εξωτερική πολυπλοκότητα καλωδίωσης και εξασφαλίζοντας ότι όλες οι συσκευές λαμβάνουν συγχρονισμένα δεδομένα διαμόρφωσης.

Προδιαγραφές XCV200-6FG456C

|

Τύπος |

Παράμετρος |

|

Κατασκευαστής |

AMD Xilinx

|

|

Σειρά |

Virtex® |

|

Συσκευασία |

Δίσκος |

|

Κατάσταση μέρους |

Απηρχαιωμένος |

|

Αριθμός εργαστηρίων/CLB |

1176 |

|

Αριθμός λογικών στοιχείων/κυττάρων |

5292 |

|

Συνολικά κομμάτια μνήμης RAM |

57344 |

|

Αριθμός I/O |

284 |

|

Αριθμός πύλων |

236666 |

|

Τάση - προμήθεια |

2.375V ~ 2.625V |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Θερμοκρασία λειτουργίας |

0 ° C ~ 85 ° C (TJ) |

|

Πακέτο / θήκη |

456-BBGA |

|

Πακέτο συσκευών προμηθευτή |

456-FBGA (23x23) |

|

Αριθμός προϊόντος βάσης |

XCV200 |

Εφαρμογές XCV200-6FG456C

Τηλεπικοινωνίες και δικτύωση

Οι XCV200-6FG456C υπερέχουν στις εφαρμογές τηλεπικοινωνιών και δικτύωσης λόγω της ικανότητάς του να χειρίζεται τις μεταδόσεις δεδομένων υψηλής ταχύτητας και τις πολύπλοκες εργασίες επεξεργασίας σήματος.Οι υψηλές δυνατότητες της πύλης και οι ισχυρές δυνατότητες I/O του επιτρέπουν να υποστηρίζουν λειτουργίες όπως επεξεργασία πακέτων, διαμόρφωση σήματος/αποδιαμόρφωση και πρωτόκολλα διόρθωσης σφαλμάτων.

Ψηφιακή επεξεργασία σήματος (DSP)

Ιδανικό για εφαρμογές DSP, αυτό το FPGA μπορεί να εκτελέσει ταχείες και πολύπλοκες μαθηματικούς υπολογισμούς που απαιτούνται στις τεχνολογίες επεξεργασίας ήχου και βίντεο.Είτε πρόκειται για συστήματα πολυμέσων, αναγνώρισης φωνής ή υπηρεσιών ροής, τις ισχυρές δυνατότητες επεξεργασίας του XCV200-6FG456C και την αποδοτική επεξεργασία σήματος υψηλής ποιότητας.

Βιομηχανικά συστήματα ελέγχου

Στη βιομηχανική αυτοματοποίηση, το XCV200-6FG456C παρέχει την απαραίτητη απόδοση για τη διαχείριση συστημάτων ελέγχου και δίκτυα αυτοματισμού.Η ικανότητά του να εκτελεί ταυτόχρονα πολλαπλές εργασίες ελέγχου, εξασφαλίζοντας ταυτόχρονα τους χρόνους απόκρισης, το καθιστά κατάλληλο για εφαρμογές στον έλεγχο των διαδικασιών, τη ρομποτική και την όραση της μηχανής.

Ιατρικά όργανα

Η ακρίβεια και η ταχύτητα του FPGA είναι εξαιρετικές στην ιατρική απεικόνιση και τον διαγνωστικό εξοπλισμό, όπου βοηθά στην επεξεργασία σύνθετων αλγορίθμων για εφαρμογές απεικόνισης όπως η μαγνητική τομογραφία, ο υπερήχων και οι CT σαρώσεις.Οι δυνατότητες του XCV200-6FG456C εξασφαλίζουν ότι μπορεί να χειριστεί υψηλή απόδοση δεδομένων και περίπλοκη επεξεργασία που απαιτείται στη σύγχρονη ιατρική τεχνολογία.

XCV200-6FG456C παρόμοια μέρη

XCV200-6FG456C Βήματα προγραμματισμού

Βήματα προγραμματισμού για το XCV200-6FG456C:

1. Εισαγωγή σχεδιασμού

Η αρχική φάση του προγραμματισμού FPGA περιλαμβάνει τον ορισμό της ψηφιακής λογικής και της λειτουργικότητας του συστήματός σας.Αυτό μπορεί να γίνει χρησιμοποιώντας γλώσσες περιγραφής υλικού (HDL) όπως το VHDL ή το Verilog, όπου γράφετε κώδικα που καθορίζει τον τρόπο με τον οποίο το FPGA επεξεργάζεται δεδομένα και αλληλεπιδρά με άλλο υλικό.Τα εργαλεία σχηματικής εισόδου που είναι διαθέσιμα σε λογισμικό σχεδιασμού FPGA όπως το Xilinx ISE ή το Vivado μπορούν να χρησιμοποιηθούν.Αυτή η μέθοδος περιλαμβάνει τη δημιουργία μιας οπτικής αναπαράστασης της λογικής, μεταφέροντας και πέφτουν τα εξαρτήματα, τα οποία κάποιοι βρίσκουν πιο διαισθητικά από τον κωδικό γραφής.

2. Σύνθεση

Μόλις ολοκληρωθεί ο σχεδιασμός, το επόμενο βήμα είναι η σύνθεση, όπου ένα εργαλείο όπως η τεχνολογία XST (Xilinx Synthesis) της Xilinx μετατρέπει τον κώδικα HDL ή τον σχηματικό σχεδιασμό σας σε ένα netlist.Αυτό το netlist περιγράφει το κύκλωμα από την άποψη των γενικών ψηφιακών εξαρτημάτων, όπως οι λογικές πύλες και τα μητρώα.Η διαδικασία σύνθεσης περιλαμβάνει επίσης τη βελτιστοποίηση του σχεδιασμού για την ικανοποίηση των απαιτήσεων απόδοσης και την ελαχιστοποίηση της χρήσης των πόρων για την αποτελεσματική λειτουργία FPGA.

3. Εφαρμογή

Η διαδικασία εφαρμογής ξεκινά με μετάφραση, συνδυάζοντας το σχεδιασμό σας με αρχεία περιορισμού που καθορίζουν παραμέτρους όπως συχνότητες ρολογιών και αναθέσεις ακίδων.Μετά τη μετάφραση, το στάδιο χαρτογράφησης αναθέτει τα στοιχεία του netlist σας σε συγκεκριμένους φυσικούς πόρους στο FPGA, όπως οι πίνακες αναζήτησης (LUTS) και τα σαγιονάρες.Η φάση τοποθέτησης και δρομολόγησης καθορίζει τότε τις φυσικές θέσεις κάθε συστατικού μέσα στην αρχιτεκτονική του FPGA και καθορίζει τις συνδέσεις μεταξύ τους μέσω προγραμματιζόμενων πόρων διασύνδεσης.Αυτό το στάδιο είναι ιδανικό για την επίτευξη των επιθυμητών μετρήσεων απόδοσης, συμπεριλαμβανομένων των συχνοτήτων ρολογιών.

4. Bitstream Generation

Μετά την επιτυχή τοποθέτηση και δρομολόγηση, το εργαλείο δημιουργεί ένα bitstream, ένα αρχείο δυαδικών ρυθμίσεων που περιέχει όλες τις πληροφορίες προγραμματισμού για το FPGA.Συχνά συνιστάται η προσομοίωση του τελικού σχεδιασμού μετά την τοποθέτηση για να εξασφαλιστεί ότι το bitstream θα συμπεριφέρεται όπως αναμένεται υπό συνθήκες.Αυτό το βήμα επαλήθευσης βοηθά στην αποφυγή πιθανών ζητημάτων κατά τη διάρκεια της πραγματικής λειτουργίας.

5. Διαμόρφωση

Το τελικό βήμα περιλαμβάνει τη φόρτωση του bitstream στο FPGA χρησιμοποιώντας διάφορες μεθόδους διαμόρφωσης.Η λειτουργία Slave-Serial, μια απλή και οικονομικά αποδοτική επιλογή, ρυθμίζει το FPGA μέσω μιας εξωτερικής κύριας συσκευής που στέλνει σειριακά δεδομένα.Σε λειτουργία Master-Serial, το FPGA διαβάζει αυτόνομα το bitstream από ένα συνημμένο σειριακό χορό.Για διαμορφώσεις υψηλής ταχύτητας, η λειτουργία SelectMap επιτρέπει σε έναν εξωτερικό μικροεπεξεργαστή να φορτώσει δεδομένα στο FPGA γρήγορα.Επιπλέον, η λειτουργία JTAG χρησιμοποιείται όχι μόνο για προγραμματισμό αλλά και για δοκιμή και εντοπισμό σφαλμάτων, χρησιμοποιώντας μια τυπική διεπαφή για προγραμματισμό στο σύστημα και δοκιμές οριακής σάρωσης.

XCV200-6FG456C Πλεονεκτήματα

Εκτέλεση

Η σειρά Xilinx Virtex, στην οποία ανήκει το XCV200-6FG456C, βελτιστοποιείται για επιδόσεις υψηλής ταχύτητας, προσφέροντας ρυθμούς ρολογιού συστήματος μέχρι 200 MHz.Αυτό το καθιστά κατάλληλο για εφαρμογές που απαιτούν γρήγορη επεξεργασία δεδομένων, εξασφαλίζοντας αποτελεσματικό χειρισμό σύνθετων αλγορίθμων και λειτουργιών υψηλής ταχύτητας όπως τηλεπικοινωνίες, επεξεργασία και πολυμέσων.

Υποστήριξη προτύπων I/O

Αυτό το FPGA υποστηρίζει ένα ευρύ φάσμα προτύπων εισόδου/εξόδου, συμπεριλαμβανομένων των LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT και AGP.Τέτοιες εκτεταμένες υποστήριξης των προτύπων I/O επιτρέπουν στο XCV200-6FG456C να ενσωματωθεί απρόσκοπτα με διάφορα εξαρτήματα του συστήματος, ενισχύοντας τη χρησιμότητά του σε διάφορα ψηφιακά οικοσυστήματα.Αυτή η ευελιξία επιτρέπει την προσαρμογή του FPGA σε διαφορετικές συνθήκες διασύνδεσης χωρίς τροποποιήσεις του συστήματος.

Διαχείριση ρολογιού

Το XCV200-6FG456C ενσωματώνει πολλαπλούς βρόχους κλειδώματος καθυστέρησης (DLL) για κατανομή και διαχείριση ρολογιού στο σύστημα.Αυτά τα DLL βοηθούν στη βελτίωση του χρονισμού και της αξιοπιστίας του συστήματος παρέχοντας απαραίτητα σήματα ρολογιού που είναι απαραίτητα για σύγχρονες λειτουργίες.Αυτή η λειτουργία είναι σημαντική για τη μείωση των σφαλμάτων του συστήματος και την ενίσχυση της συνολικής απόδοσης, ιδιαίτερα σε σύνθετα σχέδια που απαιτούν ακριβή χρονισμό και συγχρονισμό.

Ευελιξία σχεδιασμού

Με 1.176 διαμορφώσιμα λογικά μπλοκ και 5.292 λογικά κύτταρα, το XCV200-6FG456C προσφέρει σημαντικούς λογικούς πόρους με την ικανότητα να εφαρμόσει ένα ευρύ φάσμα λειτουργιών.Από την απλή λογική κόλλας σε περίπλοκα ψηφιακά συστήματα, αυτό το FPGA υποστηρίζει πολύπλοκες απαιτήσεις σχεδιασμού, καθιστώντας την ιδανική για εφαρμογές στον προσαρμοσμένο υπολογισμό, την επεξεργασία ψηφιακού σήματος και την πρωτοτύπωση.

Ταχεία πρωτότυπα

Τα FPGAs όπως το XCV200-6FG456C είναι γνωστά για την ικανότητά τους να υποστηρίξουν ταχεία πρωτότυπα.Αυτή η συσκευή επιτρέπει τις επαναλήψεις γρήγορου σχεδιασμού και μπορεί να αναδιαμορφωθεί στο πεδίο, το οποίο αποτελεί πλεονέκτημα για τους κύκλους ανάπτυξης καθώς μειώνει το χρόνο στην αγορά.Προσαρμόζεται επίσης αποτελεσματικά στις μεταβαλλόμενες απαιτήσεις ή ενημερώσεις στις προδιαγραφές του έργου, διασφαλίζοντας ότι τα τελικά προϊόντα είναι ενημερωμένα με τα τελευταία τεχνολογικά πρότυπα.

Δυνατότητα ολοκλήρωσης

Οι δυνατότητες ενσωμάτωσης του XCV200-6FG456C διευκολύνουν την ενοποίηση πολλαπλών διακριτών εξαρτημάτων σε ένα μόνο τσιπ.Αυτή η ενσωμάτωση μπορεί να οδηγήσει σε μειωμένη πολυπλοκότητα του συστήματος, χαμηλότερη κατανάλωση ενέργειας και εξοικονόμηση κόστους.Με την ελαχιστοποίηση του αριθμού των απαιτούμενων χωριστών στοιχείων, αυτό το FPGA απλοποιεί τις διαδικασίες σχεδιασμού και βελτιώνει την αξιοπιστία και τη συμπαγής του συνολικού συστήματος.

Διαστάσεις συσκευασίας XCV200-6FG456C

Το XCV200-6FG456C είναι μια προγραμματιζόμενη συστοιχία πύλης (FPGA) από τη σειρά Virtex® της AMD, που φιλοξενείται σε ένα πακέτο πλέγματος πλέγματος πλέγματος (FBGA) 456 μπάλας (FBGA).

• Τύπος πακέτου: 456-FBGA

• Μέγεθος πακέτου: 23 mm x 23 mm

• Βήμα: 1,0 mm

XCV200-6FG456C Κατασκευαστής

Το XCV200-6FG456C είναι μια προγραμματιζόμενη συστοιχία πύλης (FPGA) που αναπτύχθηκε αρχικά από την Xilinx, μια εταιρεία γνωστή για τις προγραμματιζόμενες λογικές συσκευές υψηλής απόδοσης.Μετά την απόκτηση του Xilinx από Amd, το XCV200-6FG456C συνδέεται τώρα με την AMD ως τον σημερινό κατασκευαστή του.Ωστόσο, αυτό το μοντέλο FPGA είναι παρωχημένο και δεν είναι πλέον σε παραγωγή.Η AMD συνεχίζει να υποστηρίζει τις νεότερες αρχιτεκτονικές FPGA με βελτιωμένη απόδοση, απόδοση ενέργειας και εκτεταμένη μακροζωία, καθιστώντας τις σύγχρονες εναλλακτικές λύσεις προτιμώμενες για νέα σχέδια.

Σύναψη

Το XCV200-6FG456C είναι ένα ευέλικτο και υψηλής ταχύτητας FPGA, χρήσιμο για πολλές εφαρμογές τεχνολογίας.Ενώ δεν γίνεται πλέον, εξακολουθεί να είναι μια καλή επιλογή για παλαιότερα συστήματα που χρειάζονται αξιόπιστη απόδοση.Αυτός ο οδηγός έχει καλύψει το σχεδιασμό, τα βήματα προγραμματισμού και τις πρακτικές χρήσεις, καθιστώντας ευκολότερη την κατανόηση του τρόπου λειτουργίας και του τρόπου με τον οποίο μπορεί να χρησιμοποιηθεί.Καθώς τα νεότερα FPGAs γίνονται διαθέσιμα, μπορείτε να χρησιμοποιήσετε αυτές τις γνώσεις για να επιλέξετε το σωστό FPGA για τις ανάγκες σας και να βελτιώσετε τα ψηφιακά σχέδια.

Φύλλο δεδομένων PDF

XCV200-6FG456C δελτίο δεδομένων:

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Συχνές ερωτήσεις [FAQ]

1. Ποια είναι η κατανάλωση ενέργειας του XCV200-6FG456C;

Το XCV200-6FG456C λειτουργεί σε 2,5V, με εύρος τάσης 2,375V έως 2,625V.Η κατανάλωση ενέργειας εξαρτάται από τη χρήση λογικής και τη συχνότητα ρολογιού, αλλά ως παλαιότερο FPGA, μπορεί να είναι λιγότερο αποδοτικό από τις νεότερες συσκευές Xilinx.Πρέπει να ληφθεί υπόψη η σωστή διαχείριση ισχύος και η διάχυση της θερμότητας.

2. Πώς συγκρίνεται το XCV200-6FG456C με το XCV200-6FG256C;

Το XCV200-6FG456C έχει ένα μεγαλύτερο πακέτο (456-ball FBGA) σε σύγκριση με την XCV200-6FG256C (256-ball FBGA), προσφέροντας περισσότερες ακίδες I/O (284 έναντι 172) και ενδεχομένως καλύτερες επιδόσεις για εφαρμογές που απαιτούν εκτεταμένη διεστροφή.Εάν ο σχεδιασμός σας βασίζεται σε περισσότερες δυνατότητες εισόδου/εξόδου, το XCV200-6FG456C είναι η καλύτερη επιλογή.

3. Μπορώ να επαναπρογραμματίσω το XCV200-6FG456C πολλές φορές;

Ναι, το XCV200-6FG456C είναι ένα FPGA με βάση το SRAM, που σημαίνει ότι μπορεί να επαναπρογραμματιστεί ένας απεριόριστος αριθμός φορές όσο παρέχεται ισχύς.Ωστόσο, θα χρειαστείτε εξωτερική μη πτητική μνήμη (EEPROM ή FLASH) για να διατηρήσετε το bitstream μετά από έναν κύκλο ισχύος.

4. Το XCV200-6FG456C υποστηρίζει σειριακή επικοινωνία υψηλής ταχύτητας;

Τα XCV200-6FG456C υποστηρίζουν πολλαπλά πρότυπα I/O όπως LVTTL, LVCMOS, PCI, GTL, HSTL και SSTL, αλλά δεν διαθέτουν ενσωματωμένα Serdes υψηλής ταχύτητας (Serializer/Deserializer) ή πομποδέκτες όπως οι σύγχρονοι FPGAs.Για εφαρμογές που απαιτούν σειριακές συνδέσεις υψηλής ταχύτητας (π.χ. PCIE, Gigabit Ethernet ή HDMI), θεωρήστε νεότερα μοντέλα FPGA.

5. Πώς συγκρίνεται το XCV200-6FG456C με τα νεότερα μοντέλα FPGA;

Το XCV200-6FG456C ανήκει σε μια παλαιότερη γενιά FPGAs.Σε σύγκριση με τα σύγχρονα FPGA της Virtex, έχει χαμηλότερο αριθμό πύλης, βραδύτερες ταχύτητες ρολογιού και περιορισμένη απόδοση ισχύος.Τα νεότερα μοντέλα προσφέρουν υψηλότερη λογική πυκνότητα, πιο ενσωματωμένη μνήμη, προηγμένα μπλοκ DSP και χαμηλότερη κατανάλωση ενέργειας, καθιστώντας τα καλύτερα για τις σύγχρονες εφαρμογές.

AD73322AR PINOUT, Χαρακτηριστικά και Τεχνικές λεπτομέρειες Εξηγούνται

στο 2025/03/21

EP20K100EFC324-1X FPGA: Χαρακτηριστικά, Προδιαγραφές, Εφαρμογές και Οδηγός Προγραμματισμού

στο 2025/03/20

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/18 147764

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/18 111989

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/18 111351

-

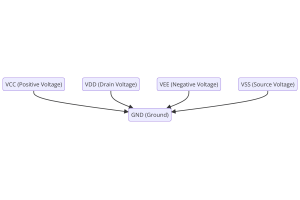

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/18 83751

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79546

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66949

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63093

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63028

-

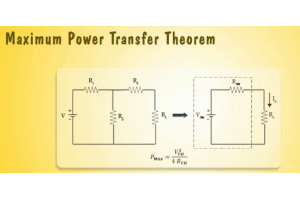

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54092

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52172