XC2S50-5TQG144I FPGA: Χαρακτηριστικά, Προδιαγραφές, Εφαρμογές και Οδηγός Προγραμματισμού

Το XC2S50-5TQG144I είναι μια ευέλικτη και ισχυρή FPGA (προγραμματιζόμενη συστοιχία πύλης) από την οικογένεια Spartan-II της AMD Xilinx.Έχει σχεδιαστεί για ψηφιακά έργα που χρειάζονται προσαρμογή, ταχύτητα και αξιοπιστία.Αυτός ο οδηγός εξηγεί τα χαρακτηριστικά, τις προδιαγραφές, τη διαδικασία προγραμματισμού και τις χρήσεις αυτού του FPGA για να σας βοηθήσουμε να καταλάβετε πώς να αξιοποιήσετε στο έπακρο.Κατάλογος

Επισκόπηση XC2S50-5TQG144I

Ο XC2S50-5TQG144I είναι ένα Spartan-II FPGA από την AMD Xilinx, σχεδιασμένη για ψηφιακά έργα που χρειάζονται ευελιξία και απόδοση.Έχει 50.000 πύλες συστήματος και 1.728 λογικά κύτταρα, επιτρέποντάς του να χειρίζεται σύνθετες εργασίες.Το τσιπ περιλαμβάνει 384 διαμορφώσιμα λογικά μπλοκ (CLBS) και 32.768 κομμάτια μνήμης RAM, δίνοντάς του καλή μνήμη και ισχύ επεξεργασίας.Με 92 ακροδέκτες εισόδου/εξόδου (I/O), μπορεί εύκολα να συνδεθεί με άλλα εξαρτήματα.Έρχεται σε ένα τετράγωνο πακέτο Quad Flat 144 ακίδων (TQFP), το οποίο είναι συμπαγές και εύκολο στη χρήση.Το FPGA τρέχει σε 2,5V (με ασφαλή περιοχή 2,375V έως 2,625V) και λειτουργεί καλά σε θερμοκρασίες μεταξύ -40 ° C και +100 ° C.Αυτό το Spartan-II FPGA είναι κατασκευασμένο με τεχνολογία 0,18-micron, καθιστώντας την αποτελεσματική και αξιόπιστη.Είναι προγραμματιζόμενο, που σημαίνει ότι μπορείτε να ενημερώσετε τις λειτουργίες του ανάλογα με τις ανάγκες.

Για μια οικονομικά αποδοτική λύση υψηλής απόδοσης, η τοποθέτηση μιας τάξης χύδην μαζί μας είναι η βέλτιστη επιλογή, εξασφαλίζοντας ανώτερη ποιότητα.

XC2S50-5TQG144I Μοντέλα CAD

XC2S50-5TQG144I Σύμβολο

XC2S50-5TQG144I αποτύπωμα

XC2S50-5TQG144I 3D μοντέλο

Χαρακτηριστικά XC2S50-5TQG144I

• Πύλες συστήματος: Το XC2S50-5TQG144I FPGA προσφέρει περίπου 50.000 πύλες συστήματος.Αυτό του επιτρέπει να υποστηρίζει σύνθετα ψηφιακά σχέδια και εφαρμογές που απαιτούν σημαντική ποσότητα δυνατοτήτων λογικής επεξεργασίας.

• Λογικά κύτταρα: Αυτή η συσκευή περιλαμβάνει 1.728 λογικά κύτταρα, τα οποία διευκολύνουν την εφαρμογή περίπλοκων λογικών διαμορφώσεων και δημιουργώντας διάφορες ψηφιακές λειτουργίες εντός του FPGA.

• Διαμορφώσιμα μπλοκ λογικής (CLBS): Διαθέτει 384 διαμορφώσιμα λογικά μπλοκ (CLBS), παρέχοντας τα θεμέλια για τη λογική του FPGA.Αυτά τα μπλοκ μπορούν να προγραμματιστούν και να αναδιαμορφωθούν για να ικανοποιήσουν συγκεκριμένες απαιτήσεις σχεδιασμού, ενισχύοντας τη συνολική ευελιξία της συσκευής.

• ΕΜΒΟΛΟ: Το FPGA είναι εξοπλισμένο με 32.768 bits εσωτερικής μνήμης RAM, προσφέροντας αποτελεσματικές δυνατότητες αποθήκευσης και ανάκτησης δεδομένων για εργασίες που αφορούν χειρισμό δεδομένων και προσωρινή αποθήκευση δεδομένων.

• I/O καρφίτσες: Με 92 ακροδέκτες I/O, το XC2S50-5TQG144I εξασφαλίζει άφθονη εξωτερική συνδεσιμότητα, επιτρέποντάς του να διασυνδέεται με άλλες συσκευές και εξαρτήματα σε ένα σύστημα ολοκληρωμένης ολοκλήρωσης του συστήματος.

• Τάση λειτουργίας: Η συσκευή λειτουργεί σε ονομαστική τάση 2,5V, με αποδεκτό εύρος από 2,375V έως 2,625V.Αυτό το εύρος τάσης βοηθά στην εξασφάλιση σταθερής λειτουργίας και αξιόπιστης απόδοσης υπό διάφορες ηλεκτρικές συνθήκες.

• Κλίμακα θερμοκρασίας: Το XC2S50-5TQG144I έχει σχεδιαστεί για να λειτουργεί αποτελεσματικά σε ευρύ φάσμα θερμοκρασίας, από -40 ° C έως +100 ° C, καθιστώντας την κατάλληλη για ανάπτυξη σε περιβάλλοντα με προκλητικές θερμικές συνθήκες.

XC2S50-5TQG144I Διάγραμμα μπλοκ

Το διάγραμμα δείχνει πώς τα σήματα κινούνται μέσα και έξω από το XC2S50-5TQG144I FPGA.Εξηγεί πώς το τσιπ χειρίζεται τα σημάδια εισόδου και εξόδου για να επικοινωνεί με άλλα εξαρτήματα.Στο πλευρά εξόδου , τα σήματα προέρχονται από το εσωτερικό του FPGA και περνούν από μονάδες αποθήκευσης που ονομάζονται flip-flops.Αυτά τα flip-flops κρατούν δεδομένα και βεβαιωθείτε ότι τα σήματα αλλάζουν την κατάλληλη στιγμή.Τα σήματα στη συνέχεια περνούν από ένα προγραμματιζόμενο buffer εξόδου, το οποίο ρυθμίζει πόσο ισχυρό είναι το σήμα και ελέγχει πόσο γρήγορα αλλάζει.Υπάρχει επίσης ένας διακόπτης (έλεγχος OE) που αποφασίζει εάν η έξοδος πρέπει να είναι ενεργή ή να παραμείνει μακριά.Ένα κύκλωμα προστασίας αποτρέπει τη ζημιά από τη στατική ηλεκτρική ενέργεια πριν το σήμα φτάσει στις ακίδες I/O, οι οποίες συνδέονται με άλλες συσκευές.Στο πλευρά εισόδου, σήματα από το εξωτερικό εισάγετε μέσω του προγραμματιζόμενου buffer εισόδου, το οποίο τα επεξεργάζεται πριν τα στέλνει μέσα στο FPGA.Μια προγραμματιζόμενη μονάδα καθυστέρησης βοηθά στη ρύθμιση του χρονισμού σήματος, ώστε όλα να παραμένουν σε συγχρονισμό.Το FPGA μπορεί επίσης να χρησιμοποιήσει μια εσωτερική τάση αναφοράς (VREF) για να ταιριάζει με διαφορετικά επίπεδα τάσης, καθιστώντας ευκολότερη την εργασία με διαφορετικούς τύπους κυκλωμάτων.Ορισμένες καρφίτσες εισόδου/εξόδου μοιράζονται αυτήν την αναφορά τάσης για να διατηρούν σταθερά σήματα.Αυτός ο σχεδιασμός βοηθά το FPGA να διαχειρίζεται αποτελεσματικά τα σήματα, εξασφαλίζοντας τον κατάλληλο χρονισμό, προστασία και συμβατότητα με διαφορετικά ηλεκτρονικά εξαρτήματα.

Προδιαγραφές XC2S50-5TQG144I

|

Τύπος |

Παράμετρος |

|

Κατασκευαστής |

AMD Xilinx |

|

Σειρά |

Spartan®-II |

|

Συσκευασία |

Δίσκος |

|

Κατάσταση μέρους |

Απηρχαιωμένος |

|

Αριθμός εργαστηρίων/CLB |

384 |

|

Αριθμός λογικών στοιχείων/κυττάρων |

1728 |

|

Συνολικά κομμάτια μνήμης RAM |

32.768 |

|

Αριθμός I/O |

92 |

|

Αριθμός πύλων |

50.000 |

|

Τάση - προμήθεια |

2.375V ~ 2.625V |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Θερμοκρασία λειτουργίας |

-40 ° C ~ 100 ° C (TJ) |

|

Πακέτο / θήκη |

144-LQFP |

|

Πακέτο συσκευών προμηθευτή |

144-TQFP (20x20) |

|

Αριθμός προϊόντος βάσης |

XC2S50 |

Εφαρμογές XC2S50-5TQG144I

Ενσωματωμένα συστήματα

Στα ενσωματωμένα συστήματα, το XC2S50-5TQG144I παρέχει την απαραίτητη λογική για εφαρμογές που βασίζονται σε μικροελεγκτές.Χρησιμοποιείται εκτενώς στην αυτοκινητοβιομηχανία, τις φορητές συσκευές και τη ρομποτική μικρής κλίμακας για την ενίσχυση της λειτουργικότητας και της ανταπόκρισης.

Επεξεργασία σήματος

Το FPGA υπερέχει σε εργασίες επεξεργασίας σήματος, όπου απαιτείται η ικανότητά του να εκτελεί παράλληλη επεξεργασία.Είναι ιδανικό για επεξεργασία ήχου και βίντεο, τηλεπικοινωνίες και ανάλυση δεδομένων, παρέχοντας την ιπποδύναμη για την αντιμετώπιση σύνθετων αλγορίθμων και ροών δεδομένων υψηλής ταχύτητας.

Βιομηχανικά συστήματα ελέγχου

Τα βιομηχανικά συστήματα ελέγχου επωφελούνται από την ευρωστία και την προγραμματισμό της FPGA, καθιστώντας την κατάλληλη για εφαρμογές όπως ο έλεγχος της διαδικασίας, η αυτοματοποίηση των μηχανών και η παρακολούθηση του συστήματος.Η αξιοπιστία του εξασφαλίζει συνεπή απόδοση σε περιβάλλοντα που απαιτούν ακρίβεια και επιχειρησιακή σταθερότητα.

Συστήματα επικοινωνίας

Στα συστήματα επικοινωνίας, το XC2S50-5TQG144I βοηθά στη διαχείριση της μετάδοσης και λήψης δεδομένων, των δραστηριοτήτων υποστήριξης, όπως η διαμόρφωση σήματος και η αποδιαμόρφωση, η μετατροπή του πρωτοκόλλου και η δρομολόγηση δικτύου.Η προσαρμοστικότητά του είναι το κλειδί στις εξελισσόμενες τηλεπικοινωνιακές υποδομές και τις αναδυόμενες ασύρματες τεχνολογίες.

Πρωτότυπα και ανάπτυξη

Το FPGA χρησιμοποιείται επίσης εκτενώς για τα ψηφιακά κυκλώματα πρωτοτύπων.Πολλοί το χρησιμοποιούν για να δοκιμάσουν και να βελτιώσουν τις ιδέες τους πριν από την τελική παραγωγή, ειδικά σε σύνθετα έργα σχεδιασμού ASIC και Custom Chip.Αυτή η δυνατότητα μειώνει το χρόνο και το κόστος ανάπτυξης, επιταχύνοντας την πορεία από την έννοια στην αγορά.

XC2S50-5TQG144I Παρόμοια μέρη

XC2S50-5TQG144I Πλεονεκτήματα

Αποδοτικότητα κόστους

Το XC2S50-5TQG144I ξεχωρίζει για την οικονομική προσιτότητα του, παρέχοντας περισσότερα χαρακτηριστικά ανά δολάριο από πολλά ανταγωνιστικά FPGAs.Αυτή η σχέση κόστους-αποτελεσματικότητας επιτυγχάνεται μέσω της προηγμένης τεχνολογίας διαδικασιών και μιας αποτελεσματικής αρχιτεκτονικής, επιτρέποντας την ευρύτερη ανάπτυξη σε αγορές ευαίσθητου στο κόστος.

I/O υψηλής απόδοσης και συσκευασία

Αυτό το FPGA υποστηρίζει ένα ευρύ φάσμα προτύπων εισόδου/εξόδου και διατίθεται σε διάφορες οικονομικά αποδοτικές επιλογές συσκευασίας.Αυτά τα χαρακτηριστικά διασφαλίζουν ότι η συσκευή μπορεί να ενσωματωθεί σε πολλαπλές εφαρμογές χωρίς να θυσιάζεται η απόδοση, καθιστώντας την ιδανική τόσο για αγορές υψηλού επιπέδου όσο και για όγκους, όπου η ευελιξία και οι φυσικοί περιορισμοί της διασύνδεσης είναι παράγοντες.

Χαρακτηριστικά σε επίπεδο συστήματος

Εξοπλισμένα με προηγμένες λειτουργίες διαχείρισης μνήμης, όπως κατανεμημένη μνήμη RAM και διαμορφώσιμη μνήμη RAM, το XC2S50-5TQG144I ενισχύει την αποτελεσματικότητα χειρισμού των δεδομένων.Αυτά τα χαρακτηριστικά διευκολύνουν τις πολύπλοκες εργασίες αποθήκευσης και επεξεργασίας δεδομένων, ενισχύοντας τη συνολική απόδοση και την επεκτασιμότητα του συστήματος.

Επαναπρογραμματισμός

Ο επαναπρογραμματισμός του XC2S50-5TQG144I επιτρέπει απεριόριστες τροποποιήσεις στη διαμόρφωσή του, η οποία είναι ευεργετική κατά τη διάρκεια της φάσης ανάπτυξης.Αυτή η ευελιξία επιτρέπει τη βελτίωση των σχεδίων μέσω επαναληπτικών ενημερώσεων χωρίς πρόσθετο κόστος υλικού, προώθηση της καινοτομίας και μείωσης του χρόνου στο τελικό προϊόν.

XC2S50-5TQG144I Βήματα προγραμματισμού

Ο προγραμματισμός του XC2S50-5TQG144I FPGA από τη σειρά Spartan-II της AMD Xilinx περιλαμβάνει μια δομημένη σειρά βημάτων που έχουν σχεδιαστεί για να μεταφράζουν αποτελεσματικά ένα ψηφιακό σχέδιο σε λειτουργική διαμόρφωση FPGA.Ακολουθεί ένας ολοκληρωμένος και λεπτομερής οδηγός για να σας βοηθήσει μέσω της διαδικασίας προγραμματισμού:

1. Εισαγωγή σχεδιασμού

Ξεκινήστε με τη φάση εισόδου σχεδιασμού, όπου δημιουργείτε την ψηφιακή σας λογική χρησιμοποιώντας μια γλώσσα περιγραφής υλικού (HDL), όπως VHDL ή Verilog.Αυτό το αρχικό βήμα περιλαμβάνει λεπτομερώς τη λειτουργικότητα και τη λογική που θέλετε να εφαρμόσετε στο FPGA.Απαιτείται ότι ο σχεδιασμός σας είναι ακριβής και αντιπροσωπεύει με ακρίβεια τις προβλεπόμενες λειτουργίες για να εξασφαλιστεί η επιτυχής σύνθεση και εφαρμογή.

2. Σύνθεση

Στο βήμα σύνθεσης, χρησιμοποιήστε ένα εργαλείο σύνθεσης για να μετατρέψετε τον κώδικα HDL σε ένα netlist.Ένα netlist είναι μια ανάλυση του σχεδίου σας σε μια μορφή που περιλαμβάνει διάφορα διασυνδεδεμένα λογικά στοιχεία όπως πύλες και σαγιονάρες.Αυτή η διαδικασία μεταφράζει το θεωρητικό σας σχέδιο σε ένα πρακτικό σχέδιο που μπορεί να κατανοήσει και να εφαρμόσει το FPGA.

3. Εφαρμογή

Η εφαρμογή περιλαμβάνει διάφορα υπο-βήματα: χαρτογράφηση, τοποθέτηση και δρομολόγηση.Η χαρτογράφηση εκχωρεί τα στοιχεία του netlist σας σε συγκεκριμένα λογικά μπλοκ εντός του FPGA.Η τοποθέτηση καθορίζει τις φυσικές θέσεις αυτών των μπλοκ στο τσιπ FPGA για τη βελτιστοποίηση της απόδοσης και της χρήσης των πόρων.Η δρομολόγηση συνδέει αυτά τα μπλοκ μέσω των προγραμματιζόμενων πόρων διασύνδεσης του FPGA.Αυτή η φάση εξασφαλίζει ότι ο σχεδιασμός πληροί όλους τους φυσικούς περιορισμούς και τους περιορισμούς απόδοσης.

4. Ορισμός περιορισμού

Κατά τη διάρκεια της διαδικασίας σχεδιασμού, απαιτείται ο καθορισμός περιορισμών.Οι περιορισμοί καθοδηγούν τα εργαλεία υλοποίησης καθορίζοντας απαιτήσεις όπως το χρονικό διάστημα (πόσο γρήγορα πρέπει να λειτουργούν το FPGA) και οι αναθέσεις PIN (οι οποίες ακροδέκτες στο FPGA θα συνδεθούν με διάφορα μέρη του υλικού σας).Αυτά είναι αρθρωμένα σε ένα αρχείο περιορισμών χρήστη (UCF), το οποίο βοηθά στην τελειοποίηση του σχεδίου για την ικανοποίηση συγκεκριμένων επιχειρησιακών προτύπων.

5. Δημιουργία bitstream

Μόλις περάσει με επιτυχία ο σχεδιασμός σας μέσω της φάσης εφαρμογής, το επόμενο βήμα είναι να δημιουργήσετε ένα αρχείο bitstream.Αυτό το αρχείο περιέχει όλα τα δεδομένα διαμόρφωσης που απαιτούνται από το FPGA για την εκτέλεση του σχεδιασμού.Το bitstream είναι η τελική έξοδος της διαδικασίας προγραμματισμού, που αντιπροσωπεύει την πλήρη, προγραμματισμένη κατάσταση του FPGA.

6. Προγραμματισμός συσκευών

Το τελικό βήμα είναι να φορτώσετε το bitstream στο XC2S50-5TQG144I FPGA, το οποίο μπορεί να γίνει χρησιμοποιώντας διάφορες λειτουργίες διαμόρφωσης ανάλογα με τη ρύθμισή σας.Σε Master Serial Mode, το FPGA διαβάζει αυτόνομα τα δεδομένα διαμόρφωσης από ένα συνημμένο σειριακό PROM (προγραμματιζόμενη μνήμη μόνο για ανάγνωση). Λειτουργία σειριακού σκλάβου Επιτρέπει σε μια εξωτερική κύρια συσκευή, όπως ένας μικροελεγκτής, να τροφοδοτεί σειριακά τα δεδομένα διαμόρφωσης FPGA. Λειτουργία παράλληλης σκλάβου Ενεργοποιεί τον προγραμματισμό υψηλής ταχύτητας παρέχοντας δεδομένα διαμόρφωσης παράλληλα από μια εξωτερική κύρια συσκευή.Εν τέλει, Λειτουργία σάρωσης ορίων (JTAG) Χρησιμοποιεί τη διεπαφή JTAG τόσο για τον προγραμματισμό όσο και για τις δοκιμές, καθιστώντας το χρήσιμο κατά την ανάπτυξη για επαναληπτική εντοπισμό σφαλμάτων και επαλήθευσης.

XC2S50-5TQG144I Διαστάσεις συσκευασίας

Ο XC2S50-5TQG144I είναι μια προγραμματιζόμενη συστοιχία πύλης (FPGA) από την οικογένεια Spartan-II του Xilinx, που στεγάζεται σε ένα Πακέτο 144 ακίδων Pin Thin Quad Flat Pack (TQFP).Αυτό το πακέτο μετρά 20 mm x 20 mm.

XC2S50-5TQG144I Κατασκευαστής

Το XC2S50-5TQG144I είναι ένα FPGA από την οικογένεια Spartan-II, που κατασκευάζεται από την AMD Xilinx.Xilinx, τώρα μέρος του Amd, είναι μια κορυφαία εταιρεία ημιαγωγών που ειδικεύεται σε FPGAs, Adaptive SoCs και άλλες προγραμματιζόμενες λογικές συσκευές.Το XC2S50-5TQG144I αναπτύχθηκε αρχικά κάτω από τη σειρά Xilinx Spartan-II, προσφέροντας 50.000 πύλες συστήματος και 1.728 λογικά κύτταρα, σχεδιασμένα για υψηλής απόδοσης αλλά και οικονομικά αποδοτικές εφαρμογές.Με την απόκτηση της Xilinx από την AMD, η εταιρεία συνεχίζει να υποστηρίζει προϊόντα κληρονομιάς όπως η σειρά Spartan-II ενώ προωθεί τις νεότερες αρχιτεκτονικές FPGA.Ωστόσο, το XC2S50-5TQG144I είναι ένα FPGA παλαιότερης γενιάς και μπορεί να αντιμετωπίσει ενδεχόμενη απαξίωση, καθώς η AMD Xilinx μετατοπίζει την εστίαση σε πιο προηγμένες οικογένειες FPGA.

Σύναψη

Το XC2S50-5TQG144I FPGA είναι ένα οικονομικά αποδοτικό και επαναπρογραμματισμένο τσιπ που προσφέρει εξαιρετική απόδοση και ευελιξία.Χρησιμοποιείται ευρέως σε ενσωματωμένα συστήματα, βιομηχανικά μηχανήματα και δίκτυα επικοινωνίας λόγω της επεξεργασίας υψηλής ταχύτητας και των ισχυρών επιλογών συνδεσιμότητας.Με την ικανότητά του να προγραμματίζεται και να ενημερώνεται, αυτό το FPGA βοηθά στη δοκιμή και την ανάπτυξη νέων ιδεών πριν από την τελική παραγωγή.Αν και είναι διαθέσιμα νεότερα FPGAs, αυτό το μοντέλο παραμένει μια σταθερή επιλογή για έργα που χρειάζονται μια αξιόπιστη και προσιτή λύση FPGA.Αυτός ο οδηγός παρέχει μια σαφή και απλή επισκόπηση των χαρακτηριστικών, των χρήσεων και της διαδικασίας προγραμματισμού της FPGA, καθιστώντας την πολύτιμη πηγή για όλους.

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Συχνές ερωτήσεις [FAQ]

1. Μπορώ να χρησιμοποιήσω το XC2S50-5TQG144I για εφαρμογές υψηλής ταχύτητας;

Το XC2S50-5TQG144I υποστηρίζει ταχύτητες έως και 200 MHz, καθιστώντας την κατάλληλη για τις πιο ενσωματωμένες και βιομηχανικές εφαρμογές.Ωστόσο, εάν το έργο σας απαιτεί διεπαφές υψηλής ταχύτητας όπως η μνήμη PCIE ή DDR, μπορεί να χρειαστείτε ένα πιο προηγμένο FPGA όπως η σειρά Spartan-6 ή Artix-7.

2. Πώς συγκρίνεται το XC2S50-5TQG144I με τα νεότερα Spartan-3 ή Spartan-6 FPGA;

Ενώ τα νεότερα FPGAs όπως το Spartan-3 ή το Spartan-6 προσφέρουν βελτιωμένη απόδοση, υψηλότερη λογική πυκνότητα και πρόσθετα χαρακτηριστικά, το XC2S50-5TQG144I παραμένει μια προτιμώμενη επιλογή για έργα ευαίσθητα στο κόστος με μέτρια πολυπλοκότητα.Εάν χρειάζεστε συμβατότητα κληρονομιάς ή σταθερή αλυσίδα εφοδιασμού, το XC2S50-5TQG144I είναι μια εξαιρετική επιλογή.

3. Ποια εργαλεία προγραμματισμού είναι συμβατά με το XC2S50-5TQG144I FPGA;

Το XC2S50-5TQG144I προγραμματίζεται χρησιμοποιώντας Xilinx ISE (ολοκληρωμένο περιβάλλον λογισμικού).Ενώ τα νεότερα εργαλεία Xilinx όπως το Vivado δεν υποστηρίζουν την οικογένεια Spartan-II, το ISE παρέχει όλες τις απαραίτητες λειτουργίες σχεδιασμού, σύνθεσης και προγραμματισμού για αυτό το FPGA.

4. Μπορώ να μεταφέρει ένα υπάρχον σχέδιο Σπαρτιάτης-ΙΙ σε ένα νεότερο FPGA;

Ναι, αλλά απαιτεί τροποποιήσεις.Οι νεότερες οικογένειες Spartan-3 και Spartan-6 χρησιμοποιούν διαφορετικά αρχιτεκτονικά, επίπεδα τάσης και μεθόδους διαμόρφωσης.Εάν σκέφτεστε τη μετανάστευση, μπορούμε να βοηθήσουμε στην επιλογή κατάλληλων εναλλακτικών λύσεων και στην ελαχιστοποίηση των αλλαγών σχεδιασμού.

5. Ο προγραμματισμός JTAG του XC2S50-5TQG144I υποστηρίζει;

Α: Ναι, το FPGA υποστηρίζει τον προγραμματισμό σάρωσης JTAG (IEEE 1149.1), ο οποίος επιτρέπει την εύκολη εντοπισμό σφαλμάτων και διαμόρφωσης χρησιμοποιώντας μια τυπική διεπαφή JTAG.Αυτό είναι χρήσιμο τόσο για τον αρχικό προγραμματισμό όσο και για την αναδιάταξη χωρίς εξωτερική μνήμη.

XC4013XL-3PQ240C FPGA: εναλλακτικές λύσεις, προδιαγραφές, εφαρμογές και φύλλο δεδομένων

στο 2025/03/18

Ενισχυτές ισχύος RF: Πώς λειτουργούν, ποιος τύπος είναι πιο αποτελεσματικός

στο 2025/03/18

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/18 147770

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/18 112006

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/18 111351

-

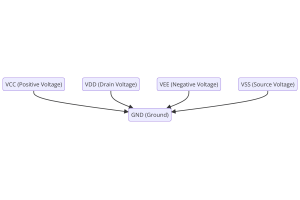

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/18 83768

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79564

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66959

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63098

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63040

-

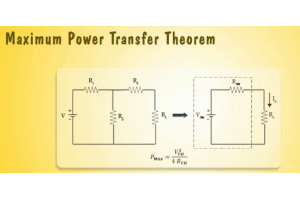

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54096

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52184