LFEC3E-3Q208C FPGA Επισκόπηση: Χαρακτηριστικά, εφαρμογές, προγραμματισμός και προδιαγραφές

Σε αυτό το άρθρο, θα μάθετε για το LFEC3E-3Q208C, ένα FPGA από το Semiconductor Lattice.Θα δείτε τι είναι, τα κύρια χαρακτηριστικά που προσφέρει και γιατί είναι χρήσιμο για πολλά σχέδια μεσαίας εμβέλειας.Το περιεχόμενο σας περνάει επίσης μέσω των προδιαγραφών, των εφαρμογών και της διαδικασίας προγραμματισμού βήμα προς βήμα, μαζί με τα πλεονεκτήματα, τα μειονεκτήματα και τα στοιχεία του κατασκευαστή.Κατάλογος

Ποιο είναι το LFEC3E-3Q208C;

Ο LFEC3E-3Q208C είναι μια οικονομικά αποδοτική συστοιχία πύλης (FPGA) από το Semiconductor του Lattice, σχεδιασμένο ως μέρος της οικογένειας Latticeec (Economy).Αυτή η οικογένεια αναπτύχθηκε για να παρέχει προγραμματιζόμενες λογικές λύσεις που εξισορροπούν την οικονομική προσιτότητα με αξιόπιστη απόδοση για τα σχέδια mainstream.Μέσα στην ιεραρχία του Latticeec, κάθεται στο μέσο της εμβέλειας, προσφέροντας περίπου 3.000 λογικά στοιχεία και αποτελεσματική χρήση ενέργειας, γεφυρώνοντας το χάσμα μεταξύ των μικρότερων συσκευών εισόδου και μεγαλύτερων, μεγαλύτερων μοντέλων.Η ευρύτερη σειρά LatticeECP/EC υπογραμμίζει την προγραμματισμό, την επεκτασιμότητα και την ευελιξία σε πολλαπλά μεγέθη συσκευών, με την παραλλαγή της ΕΚ να επικεντρώνεται στην απόδοση που βασίζεται στην οικονομία.

Ψάχνετε για LFEC3E-3Q208C;Επικοινωνήστε μαζί μας για να ελέγξετε το τρέχον απόθεμα, το χρόνο παράδοσης και την τιμολόγηση.

Χαρακτηριστικά LFEC3E-3Q208C

• Λογικοί πόροι

Η συσκευή ενσωματώνει περίπου 3.100 λογικά στοιχεία που οργανώνονται σε 384 μπλοκ, δίνοντάς της αρκετή χωρητικότητα για σχέδια μεσαίας εμβέλειας.Αυτή η ισορροπία των πόρων το καθιστά κατάλληλο για λογική ελέγχου, επεξεργασία σήματος και ενσωματωμένες εφαρμογές χωρίς υπερβολικό κόστος.

• Προγραμματιζόμενο I/O

Με έως και 145 προγραμματιζόμενες ακίδες εισόδου/εξόδου, υποστηρίζει μια μεγάλη ποικιλία επιλογών συνδεσιμότητας.Αυτά τα I/OS είναι συμβατά με πολλαπλά πρότυπα όπως LVCMOS, LVTTL, LVDS, PCI και SSTL, επιτρέποντας την ευέλικτη ολοκλήρωση του συστήματος.

• Ενσωματωμένη μνήμη

Το FPGA περιλαμβάνει ειδικό μπλοκ RAM (EBR) και κατανεμημένους πόρους RAM, παρέχοντας αποτελεσματική αποθήκευση στο τσιπ.Αυτό επιτρέπει την υλοποίηση των ρυθμίσεων δεδομένων, των πινάκων αναζήτησης ή των μικρών ενσωματωμένων αναμνήσεων απευθείας μέσα στη συσκευή.

• Διαχείριση ρολογιού

Διαθέτει έως και τέσσερα ολοκληρωμένα PLL, προσφέροντας πολλαπλασιασμό συχνότητας, διαίρεση και μετατόπιση φάσης.Αυτό επιτρέπει τον ακριβή έλεγχο του χρονισμού και τον συγχρονισμό για σχέδια υψηλής ταχύτητας.

• Υποστήριξη μνήμης DDR

Η συσκευή περιλαμβάνει υποστήριξη υλικού για διεπαφές DDR, ικανές να εκτελούν DDR400 (200 MHz).Αυτό το καθιστά πρακτικό για σχέδια που απαιτούν εξωτερική πρόσβαση μνήμης υψηλής ταχύτητας.

• Απόδοση ρεύματος

Λειτουργώντας με τροφοδοσία πυρήνα 1,2 V, το FPGA ελαχιστοποιεί τη συνολική κατανάλωση ενέργειας του συστήματος.Ο σχεδιασμός χαμηλής ισχύος είναι ιδανικός για φορητές ή ευαίσθητες σε ενέργεια εφαρμογές.

• Χαρακτηριστικά σε επίπεδο συστήματος

Ενσωματωμένες λειτουργίες όπως η σάρωση ορίων IEEE 1149.1, η ανάλυση λογικής επί τόπου (ISPTRACY) και η διεπαφή Flash Boot SPI απλοποιούν τη δοκιμή και το εντοπισμό σφαλμάτων.Αυτά τα χαρακτηριστικά μειώνουν τον χρόνο ανάπτυξης και βελτιώνουν την αξιοπιστία του σχεδιασμού.

• Στήριξη ανάπτυξης

Υποστηριζόμενη από τη σουίτα Design Isplever, η συσκευή επωφελείται από την αυτοματοποιημένη σύνθεση, το place-and-route και τα εργαλεία επαλήθευσης.Μπορείτε επίσης να χρησιμοποιήσετε τα μπλοκ IP IPSVERCORE για να επιταχύνετε τις κοινές λειτουργίες και να συντομεύσετε το χρόνο στην αγορά.

Διάγραμμα μπλοκ Family Latticeecp/EC

Το μπλοκ διάγραμμα της οικογένειας LatticeECP/EC (συμπεριλαμβανομένης της LFEC3E-3Q208C) δείχνει πώς κατασκευάζεται το FPGA και πώς λειτουργούν τα μέρη του.Τα προγραμματιζόμενα κύτταρα I/O (PICS) τοποθετούνται γύρω από τις άκρες για να συνδέσετε το τσιπ με εξωτερικές συσκευές, υποστηρίζοντας πολλά πρότυπα σημάτων.Στο εσωτερικό, οι προγραμματιζόμενες λειτουργικές μονάδες (PFU) χειρίζονται τις λογικές λειτουργίες, με κάποιες συνδυασμένες με ενσωματωμένο RAM Block (EBR) για την αποθήκευση δεδομένων και άλλων που επικεντρώνονται μόνο στη λογική.Τα Sysclock PLL διαχειρίζονται σήματα ρολογιού, ώστε ο σχεδιασμός να μπορεί να τρέξει με τη σωστή ταχύτητα και το χρονοδιάγραμμα.Η θύρα Sysconfig και η θύρα JTAG σας επιτρέπουν να προγραμματίσετε, να δοκιμάσετε και να εντοπίσετε το FPGA εύκολα.Αυτή η διάταξη δίνει την ευελιξία LFEC3E-3Q208C, την αξιόπιστη απόδοση και την απλή ενσωμάτωση σε ευαίσθητα στο κόστος σχέδια.

Διάγραμμα φέτα Latticeecp/EC

Η φέτα στην οικογένεια LatticeECP/EC, όπως στο LFEC3E-3Q208C, είναι η βασική λογική μονάδα που συνδυάζει μπλοκ LUT4 & μεταφοράς για τη λογική και τις αριθμητικές λειτουργίες.Κάθε φέτα περιλαμβάνει επίσης flip-flops/μάνδαλες για την αποθήκευση δεδομένων και την ενεργοποίηση της διαδοχικής λογικής, με πολυπλέκτες να διατρέχουν σήματα ευέλικτα είτε μέσω καταχωρητών είτε απευθείας.Αυτή η δομή είναι σημαντική επειδή δίνει την ταχύτητα, την ευελιξία και την αποτελεσματικότητα του FPGA για να χειριστεί τόσο τα απλά όσο και τα πολύπλοκα ψηφιακά σχέδια.Ο παρακάτω πίνακας συνοψίζει τις περιγραφές σήματος φέτας, συμπεριλαμβανομένων των λειτουργιών, των τύπων, των ονομάτων σήματος και των σκοπών.

|

Λειτουργία |

Τύπος |

Ονόματα σήματος |

Περιγραφή |

|

Εισαγωγή |

Σήμα δεδομένων |

A0, B0, C0, D0 |

Εισόδους στο LUT4 |

|

Εισαγωγή |

Σήμα δεδομένων |

A1, B1, C1, D1 |

Εισόδους στο LUT4 |

|

Εισαγωγή |

Πολλαπλών χρήσεων |

M0 |

Εισροή πολλαπλών χρήσεων |

|

Εισαγωγή |

Πολλαπλών χρήσεων |

M1 |

Εισροή πολλαπλών χρήσεων |

|

Εισαγωγή |

Σήμα ελέγχου |

CE |

Ενεργοποίηση ρολογιού |

|

Εισαγωγή |

Σήμα ελέγχου |

LSR |

Τοπικό σετ/επαναφορά |

|

Εισαγωγή |

Σήμα ελέγχου |

CLK |

Ρολόι συστήματος |

|

Εισαγωγή |

Σήμα inter-pfu |

Φινίρισμα |

Γρήγορη μεταφορά στο¹ |

|

Παραγωγή |

Σήματα δεδομένων |

F0, F1 |

LUT4 Εγγραφή εξόδου Μητρώο Σήματα παράκαμψης |

|

Παραγωγή |

Σήματα δεδομένων |

Q0, Q1 |

Έξοδοι εγγραφής |

|

Παραγωγή |

Σήματα δεδομένων |

OFX0 |

Έξοδος ενός LUT5 MUX |

|

Παραγωγή |

Σήματα δεδομένων |

OFX1 |

Έξοδος ενός LUT6, LUT7, LUT8 2 MUX ανάλογα με τη φέτα |

|

Παραγωγή |

Σήμα inter-pfu |

FCO |

Για το δικαίωμα περισσότερο PFU η γρήγορη έξοδος αλυσίδας μεταφοράς¹ |

Προδιαγραφές LFEC3E-3Q208C

|

Τύπος |

Παράμετρος |

|

Κατασκευαστής |

Ημιαγωγός πλέγματος |

|

Τάση - προμήθεια |

1.14V ~ 1.26V |

|

Συνολικά κομμάτια μνήμης RAM |

56,320 |

|

Πακέτο συσκευών προμηθευτή |

208-PQFP (28x28) |

|

Σειρά |

ΕΚ |

|

Πακέτο / θήκη |

208-BFQFP |

|

Πακέτο |

Δίσκος |

|

Θερμοκρασία λειτουργίας |

0 ° C ~ 85 ° C (TJ) |

|

Αριθμός λογικών στοιχείων/κυττάρων |

3.100 |

|

Αριθμός I/O |

145 |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Αριθμός προϊόντος βάσης |

LFEC3 |

Εφαρμογές LFEC3E-3Q208C

1. Συστήματα ενσωματωμένων ελέγχου

Το LFEC3E-3Q208C είναι κατάλληλο για ενσωματωμένους ελεγκτές σε συσκευές, βιομηχανική αυτοματοποίηση και πύλες IoT.Η μέτρια λογική πυκνότητα και ο σχεδιασμός χαμηλού κόστους επιτρέπουν την αντικατάσταση της λογικής σταθερής λειτουργίας με προγραμματιζόμενη ευελιξία.Αυτό διευκολύνει την αναβάθμιση των συστημάτων ή την προσαρμογή στα εξελισσόμενα πρότυπα χωρίς να επανασχεδιάζετε το υλικό.

2. Διασύνδεση μνήμης DDR

Με ενσωματωμένη υποστήριξη για τη μνήμη DDR400, η συσκευή μπορεί να διαχειριστεί τη ρύθμιση των δεδομένων, την καταγραφή ή την προσωρινή αποθήκευση σε εφαρμογές.Αυτή η λειτουργία είναι χρήσιμη σε συστήματα όπου η ταχύτητα εξωτερικής μνήμης είναι σημαντική, αλλά δεν απαιτείται πλήρης απόδοση FPGA υψηλής ποιότητας.Πολλοί επωφελούνται από την ισορροπία της ταχύτητας, του κόστους και της αποδοτικότητας της μνήμης.

3. Μετατροπή γεφύρωσης και πρωτοκόλλου I/O

Χάρη στην ευρεία υποστήριξή του για πρότυπα I/O όπως LVCMOS, LVTTL, LVDS, PCI και SSTL, το FPGA είναι αποτελεσματικό στη γεφύρωση διαφορετικών ψηφιακών διεπαφών.Μπορεί να ρυθμιστεί ώστε να μεταφράζει σήματα μεταξύ υποσυστημάτων, καθιστώντας το πολύτιμο σε σχέδια μικτής τεχνολογίας.Αυτή η ευελιξία συμβάλλει στην επέκταση της ζωής του υφιστάμενου υλικού, επιτρέποντας τη συμβατότητα με τα νέα εξαρτήματα.

4. Βιομηχανικές και υποδομές εφαρμογών

Η συσκευή μπορεί επίσης να χρησιμεύσει σε εξοπλισμό βιομηχανικής και υποδομής ευαίσθητου στο κόστος, όπου η αξιοπιστία και η μέτρια απόδοση είναι επαρκείς.Η υποστήριξή της για τη σάρωση των ορίων, την εντοπισμό σφαλμάτων και τη λειτουργία χαμηλής ισχύος καθιστά ιδανικό για συστήματα που απαιτούν αποτελεσματικότητα και εύκολη συντήρηση.Οι τυπικοί ρόλοι περιλαμβάνουν μονάδες ελέγχου, μονάδες διασύνδεσης και συστήματα παρακολούθησης.

LFEC3E-3Q208C παρόμοια μέρη

|

Προσδιορισμός |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Λογικά στοιχεία (LUTS) |

~ 3.1K |

~ 3.1K |

~ 3.1K |

~ 3.1K |

~ 1,5K |

~ 6.1K |

|

Λογικά μπλοκ |

384 |

384 |

384 |

384 |

192 |

768 |

|

Ενσωματωμένο μπλοκ RAM (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Μέγιστη συχνότητα λειτουργίας |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

Μετρήστε I/O |

145 |

145 |

145 |

145 |

112 |

145 |

|

Πακέτο |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

Τάση πυρήνα |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Κλίμακα θερμοκρασίας |

0 ° C έως +70 ° C |

-40 ° C έως +85 ° C |

0 ° C έως +70 ° C |

0 ° C έως +70 ° C |

0 ° C έως +70 ° C |

0 ° C έως +70 ° C |

|

Τύπος συμμόρφωσης / πακέτου |

Πρότυπο |

Βιομηχανικός |

Χωρίς μόλυβδο (QN) |

Παραλλαγή (q) |

Πρότυπο |

Πρότυπο |

|

Εφαρμογή |

Μεσαία πυκνότητα, γενικός σκοπός |

Ίδιο με το LFEC3E αλλά τη βιομηχανική χρήση |

Ίδιο με το LFEC3E αλλά το πακέτο συμβατό |

Ίδια οικογένεια, εύκολη μετανάστευση |

Επιλογή κόστους χαμηλής πυκνότητας |

Αναβάθμιση υψηλότερης πυκνότητας |

Βήματα προγραμματισμού LFEC3E-3Q208C

Πριν ξεκινήσετε τον προγραμματισμό του LFEC3E-3Q208C, είναι σημαντικό να προετοιμάσετε τα σωστά εργαλεία και να κατανοήσετε τη ροή του σχεδιασμού στη διαμόρφωση της συσκευής.Κάθε βήμα βασίζεται στην προηγούμενη, οπότε η προσεκτική προσοχή θα εξασφαλίσει μια ομαλή διαδικασία προγραμματισμού.

1. Προετοιμασία υλικού και λογισμικού προγραμματισμού

Ξεκινάτε με την εγκατάσταση του προγραμματιστή Diamond του Lattice ή του συστήματος ISPVM, τα οποία είναι τα επίσημα εργαλεία για αυτό το FPGA.Στη συνέχεια, ρυθμίστε το καλώδιο προγραμματισμού JTAG, όπως το HW-USBN-2B και βεβαιωθείτε ότι τα προγράμματα οδήγησης έχουν εγκατασταθεί σωστά.Αυτό το βήμα εξασφαλίζει ότι ο υπολογιστής σας είναι έτοιμος να επικοινωνεί με τη συσκευή προορισμού χωρίς σφάλματα σύνδεσης.

2. Εφαρμόστε το σχεδιασμό σας σε λογισμικό ανάπτυξης

Στη συνέχεια, δημιουργήστε ένα νέο έργο στο Diamond Lattice και επιλέξτε το LFEC3E-3Q208C ως συσκευή προορισμού σας.Στη συνέχεια, προσθέτετε τα αρχεία προέλευσης Verilog ή VHDL, εφαρμόστε τις αναθέσεις PIN και καθορίστε τυχόν περιορισμούς χρονισμού.Μόλις γίνει αυτό, συνθέσατε το σχέδιο, εκτελέστε το place-and-route και τελικά δημιουργείτε το αρχείο bitstream (.bit ή .jed) που θα χρησιμοποιηθεί για προγραμματισμό.

3. Ρυθμίστε το σκάφος και τις συνδέσεις

Τώρα, συνδέστε το καλώδιο JTAG στον πίνακα FPGA, φροντίζοντας ότι η σύνδεση γείωσης είναι ασφαλής πριν από την τοποθέτηση των γραμμών σήματος.Επιβεβαιώστε ότι οι αντιστάσεις pull-up και pull-down είναι σωστά στη θέση τους, ειδικά σε γραμμές TCK και ανοικτού αποστράγγισης.Εάν ο πίνακας σας έχει πρόσθετες ακίδες ελέγχου όπως ERASE ή ISPEN, πρέπει να τις διαμορφώσετε σωστά για να αποτρέψετε τυχαία επαναφορά κατά τη διάρκεια του προγραμματισμού.

4. Προγραμματίστε τη συσκευή

Με το υλικό έτοιμο, ξεκινήστε το εργαλείο προγραμματισμού και επιλέξτε το συνδεδεμένο καλώδιο σας.Τοποθετήστε το δημιουργημένο αρχείο bitstream και επιλέξτε την κατάλληλη λειτουργία, συνήθως JTAG, ανάλογα με τη ρύθμισή σας.Ξεκινήστε τη διαδικασία προγραμματισμού και το εργαλείο θα διαμορφώσει το FPGA ενώ επαληθεύει ότι τα δεδομένα έχουν γραφτεί σωστά.

5. Επαληθεύστε και εντοπίστε τη διαμόρφωση της διαμόρφωσης

Μετά τον προγραμματισμό, ελέγξτε τις καρφίτσες DEN ή init στο σκάφος σας για να επιβεβαιώσετε ότι το FPGA έχει διαμορφωθεί με επιτυχία.Εάν χρειαστεί, χρησιμοποιήστε τον αναλυτή λογικής ISPTRACY ή τις λειτουργίες σάρωσης ορίων για να δοκιμάσετε τη λειτουργικότητα και να επικυρώσετε τη συμπεριφορά του σήματος.Μπορείτε να επαναλάβετε τον κύκλο σχεδιασμού και προγραμματισμού όποτε απαιτούνται αλλαγές, εξασφαλίζοντας ότι το έργο σας είναι εξευγενισμένο βήμα προς βήμα.

LFEC3E-3Q208C Πλεονεκτήματα και μειονεκτήματα

Φόντα

• Χαμηλή κατανάλωση ενέργειας, κατάλληλη για ευαίσθητα στην ενέργεια σχέδια

• οικονομικά αποδοτική σε σύγκριση με τα FPGA υψηλότερης τάξης

• Απλή εργαλειοθήκη με ευκολότερη καμπύλη μάθησης

• Πεδίο αναδιαμορφώνεται για ενημερώσεις μετά την ανάπτυξη

• συμπαγές πακέτο με καλή ισορροπία πόρων

Μειονεκτήματα

• Περιορισμένη απόδοση σε σύγκριση με τα μεγαλύτερα FPGAs

• χαμηλότερη λογική και χωρητικότητα μνήμης από τις συσκευές υψηλής τεχνολογίας

• Λιγότεροι πυρήνες IP τρίτων και υποστήριξης οικοσυστήματος

• Η εργαλειοθήκη στερείται προχωρημένων χαρακτηριστικών των μεγάλων προμηθευτών

• Δεν είναι κατάλληλο για διεπαφές εξαιρετικά υψηλής ταχύτητας

Διαστάσεις συσκευασίας LFEC3E-3Q208C

|

Τύπος |

Παράμετρος |

|

Τύπος πακέτου |

208-PQFP (Πλαστικό τετράγωνο πακέτο) |

|

Μέγεθος σώματος |

28 mm × 28 mm |

|

Πίσσα |

0,5 mm |

|

Ύψος πακέτου (μέγιστο) |

~ 3,4 mm |

|

Αρίθμηση μολύβδου |

208 καρφίτσες |

|

Στυλ πακέτου |

Gull-Wing Leads (Quad) |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Κώδικας θήκης |

BFQFP-208 |

|

Πακέτο προμηθευτών |

Δίσκος |

Κατασκευαστής LFEC3E-3Q208C

Το LFEC3E-3Q208C κατασκευάζεται από Εταιρεία Semiconductor Lattice , μια εταιρεία που εδρεύει στις ΗΠΑ με έδρα το Hillsboro του Όρεγκον.Ιδρύθηκε το 1983, το Lattice ειδικεύεται στην ανάπτυξη συστοιχιών πύλης χαμηλής ισχύος και οικονομικά αποδοτικής πύλης (FPGAs) και συναφείς λύσεις.Η Εταιρεία επικεντρώνεται στην παροχή εφαρμογών στις αγορές επικοινωνιών, υπολογιστών, ηλεκτρονικών, βιομηχανικών και αυτοκινήτων.Γνωστή για την καινοτομία σε ενεργειακά αποδοτικές προγραμματιζόμενες συσκευές, το Lattice έχει καθιερωθεί ως βασικός παίκτης στη βιομηχανία FPGA, ιδιαίτερα για σχέδια που απαιτούν παράγοντες συμπαγούς μορφής, μειωμένη κατανάλωση ενέργειας και υψηλή αξιοπιστία.

Σύναψη

Το LFEC3E-3Q208C προσφέρει ένα καλό μείγμα χαμηλού κόστους, χαμηλής χρήσης ενέργειας και αρκετή λογική και μνήμη για έργα μεσαίας εμβέλειας.Υποστηρίζει πολλά πρότυπα I/O, διαθέτει ενσωματωμένο RAM και PLL και μπορεί να συνεργαστεί με τη μνήμη DDR400, καθιστώντας χρήσιμο για τον έλεγχο, τη διεπαφή και τα βιομηχανικά καθήκοντα.Ο προγραμματισμός είναι απλός με εργαλεία πλέγματος και τα επιπλέον χαρακτηριστικά εντοπισμού σφαλμάτων βοηθούν στη δοκιμή.Παρόλο που δεν μπορεί να ταιριάζει με την ταχύτητα και την ικανότητα των μεγαλύτερων FPGAs, είναι μια αξιόπιστη επιλογή για σχέδια που χρειάζονται ευελιξία, αποτελεσματικότητα και προσιτή απόδοση.

Φύλλο δεδομένων PDF

LFEC3E-3Q208C DATASHES:

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Συχνές ερωτήσεις [FAQ]

1. Το LFEC3E-3Q208C υποστηρίζει διεπαφές υψηλής ταχύτητας όπως το PCIE ή το Gigabit Ethernet;

Όχι. Το LFEC3E-3Q208C έχει σχεδιαστεί για εφαρμογές που έχουν ευαίσθητη στο κόστος, επομένως δεν περιλαμβάνουν τους εγγενείς σειριακούς πομποδέκτες υψηλής ταχύτητας.Αντ 'αυτού επικεντρώνεται σε παράλληλες διεπαφές και υποστήριξη μνήμης DDR.

2. Μπορεί το LFEC3E-3Q208C να επαναπρογραμματιστεί μετά την ανάπτυξη;

Ναί.Ως FPGA, το LFEC3E-3Q208C είναι πλήρως αναδιαμορφώσιμο, επιτρέποντας ενημερώσεις και τροποποιήσεις σχεδιασμού ακόμη και μετά την ανάπτυξη.Αυτή η ευελιξία μειώνει το μακροπρόθεσμο κόστος συντήρησης και επεκτείνει τους κύκλους ζωής των προϊόντων.

3. Πώς χειρίζεται το σφάλμα και δοκιμή του LFEC3E-3Q208C;

Η συσκευή ενσωματώνει τη σάρωση των ορίων (IEEE 1149.1), την ανάλυση λογικής επί τόπου (ISPTRACY) και την υποστήριξη SPI Boot Flash.Αυτά τα ενσωματωμένα εργαλεία απλοποιούν το σφάλμα και μειώνουν την ανάγκη για εξωτερικό υλικό δοκιμών.

4 Μπορεί το LFEC3E-3Q208C να επεκτείνει τη διάρκεια ζωής των παλαιότερων συστημάτων υλικού;

Ναι, χάρη στις ευρείες δυνατότητες γεφύρωσης και γεφύρωσης πρωτοκόλλου, μπορεί να διασυνδέει παλαιότερα συστήματα με νεότερα εξαρτήματα, βοηθώντας τις επιχειρήσεις να επεκτείνουν τη χρησιμότητα του υφιστάμενου υλικού.

5. Ποια εργαλεία προγραμματισμού απαιτούνται για το LFEC3E-3Q208C;

Προγραμματίζεται χρησιμοποιώντας το Diamond Programmer του Lattice ή το σύστημα ISPVM.Αυτά τα εργαλεία υποστηρίζουν την καταχώρηση σχεδιασμού, τη δημιουργία bitstream και τη διαμόρφωση της συσκευής, καθιστώντας τη ροή εργασίας εξορθολογισμένη.

AD73311LARS: φύλλο δεδομένων, χαρακτηριστικά, οδηγός pinout και προγραμματισμού

στο 2025/08/28

EPM1270F256C4N MAX II CPLD Επισκόπηση: Χαρακτηριστικά, προδιαγραφές και εφαρμογές

στο 2025/08/28

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/19 147782

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/19 112062

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/19 111352

-

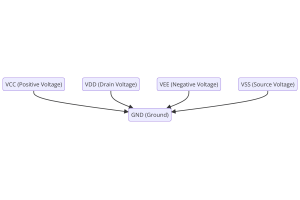

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/19 83819

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79639

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66999

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63124

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63062

-

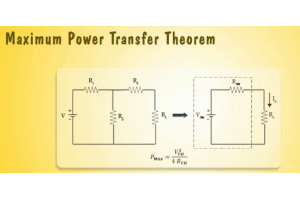

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54097

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52215