EPM7192SQC160-15 CPLD: Χαρακτηριστικά, pinout, προγραμματισμός και εφαρμογές

Αυτός ο οδηγός μιλά για το EPM7192SQC160-15, ένα προγραμματιζόμενο τσιπ λογικής από την οικογένεια Max 7000s.Εξηγεί τι μπορεί να κάνει το τσιπ, πώς λειτουργεί και πού μπορεί να χρησιμοποιηθεί.Δείχνει πώς το τσιπ είναι κατασκευασμένο μέσα, τι κάνει κάθε πείρο και πώς συνδέεται με άλλα μέρη.Ο οδηγός περιλαμβάνει επίσης το πού μπορεί να χρησιμοποιηθεί αυτό το τσιπ, πώς να το προγραμματίσετε βήμα προς βήμα, ποια άλλα παρόμοια τσιπ και ποιος το κάνει.Κατάλογος

Ποιο είναι το EPM7192SQC160-15;

Ο EPM7192SQC160-15 είναι ένα CPLD μεσαίας εμβέλειας (σύνθετη προγραμματιζόμενη λογική συσκευή) από την οικογένεια Max 7000S, που κατασκευάζεται για αξιόπιστο ψηφιακό έλεγχο λογικής σε ενσωματωμένα και βιομηχανικά συστήματα.Αυτό το τσιπ προσφέρει 192 μακροκύτταρα και περίπου 3.750 λογικές πύλες, παρέχοντας αρκετή χωρητικότητα για το χειρισμό μέτριας λογικής εργασιών.Περιλαμβάνει 124 ακροδέκτες I/O και τρέχει σε τροφοδοσία 5V, με υποστήριξη πολλαπλών I/O για τη διασύνδεση τόσο με συστήματα λογικής 3.3V και 5V.Η προγραμματιζόμενη αρχιτεκτονική που βασίζεται στο σύστημα EEPROM σημαίνει ότι μπορείτε να το επαναπρογραμματίσετε απευθείας στο κύκλωμα σας χρησιμοποιώντας το JTAG, χωρίς να χρειάζεστε επιπλέον εξαρτήματα ή εξωτερική μνήμη.Με βαθμό ταχύτητας -15, υποστηρίζει συχνότητες ρολογιών συστήματος μέχρι περίπου 76,9 MHz, προσφέροντας γρήγορη και συνεπή απόδοση χρονισμού για ευρείες ψηφιακές εφαρμογές.Η οικογένεια Max 7000S είναι γνωστή για τη σταθερή της απόδοση, τη μνήμη EEPROM και την εύκαμπτη λειτουργία τάσης.

Ψάχνετε για EPM7192SQC160-15;Επικοινωνήστε μαζί μας για να ελέγξετε το τρέχον απόθεμα, το χρόνο παράδοσης και την τιμολόγηση.

EPM7192SQC160-15 CAD Μοντέλα

EPM7192SQC160-15 Σύμβολο

EPM7192SQC160-15 Αποτύπωμα

EPM7192SQC160-15 3D μοντέλο

EPM7192SQC160-15 Χαρακτηριστικά

192 μακροκύτταρα: Η συσκευή περιλαμβάνει 192 μακροκύτταρα, τα οποία χρησιμεύουν ως βασικά προγραμματιζόμενα στοιχεία.Αυτά τα μακροκύτταρα μπορούν να ρυθμιστούν ώστε να εφαρμόσουν μια μεγάλη ποικιλία συνδυαστικών και διαδοχικών λογικών λειτουργιών που απαιτούνται σε ψηφιακά σχέδια.

Περίπου 3.750 λογικές πύλες: Προσφέρει ισοδύναμη λογική χωρητικότητα περίπου 3.750 πύλων, καθιστώντας την κατάλληλη για λογική ελέγχου μεσαίας πολυπλοκότητας, μηχανές κατάστασης ή λογική κόλλας σε ενσωματωμένα συστήματα.

Προγραμματισμός στο σύστημα μέσω JTAG: Διαθέτει μνήμη με βάση το EEPROM, η οποία επιτρέπει τον επαναπρογραμματισμό απευθείας στο σύστημα χρησιμοποιώντας μια τυπική διεπαφή JTAG, υποστηρίζοντας τόσο τα πρότυπα IEEE 1149.1 όσο και IEEE 1532.

Μέγιστη συχνότητα έως 125 MHz: Η εσωτερική λογική μπορεί να λειτουργεί με ταχύτητες ρολογιών που φθάνουν τα 125 MHz, επιτρέποντας γρήγορη επεξεργασία για εφαρμογές ευαίσθητου στο χρόνο.

Καθυστέρηση διάδοσης 7,5 ns: Το τσιπ προσφέρει καθυστέρηση χαμηλής διάδοσης περίπου 7,5 νανοδευτερόλεπτα, εξασφαλίζοντας ταχεία απόκριση σήματος από την είσοδο στην έξοδο.

Υποστηρίζει 5V τροφοδοσία με πολλαπλό I/O: Η συσκευή εκτελείται σε 5V πυρήνα και υποστηρίζει I/O πολλαπλών I/O, επιτρέποντας τη συμβατότητα τόσο με 5V και 3.3V επίπεδα σήματος για εύκολη ενσωμάτωση σε συστήματα μικτής τάσης.

Προγραμματιζόμενη ταχύτητα και έξοδοι ανοικτής αποστράγγισης: Μπορείτε να ελέγξετε τα ποσοστά άκρων σήματος για τη μείωση του EMI και να επιλέξετε εξόδους ανοικτής αποστράγγισης για μετατόπιση ενσύρματων και λογικών ή επιπέδων.

Έξι παγκόσμια παραγωγή ενεργοποιούν σήματα: Αυτά τα σήματα παγκόσμιου ελέγχου επιτρέπουν την ενεργοποίηση ή την απενεργοποίηση των εξόδων σε πολλαπλές τράπεζες I/O για αποτελεσματική διαχείριση σήματος.

Διαμορφώσιμα flip-flops σε μακροκύτταρα: Κάθε macrocell περιλαμβάνει ένα flip-flop που υποστηρίζει προκαθορισμένο, καθαρό, ρολόι και ατομικό έλεγχο, παρέχοντας βελτιωμένη ευελιξία για διαδοχικό λογικό σχεδιασμό.

Λειτουργία χαμηλής ισχύος: Η συσκευή περιλαμβάνει ένα χαρακτηριστικό εξοικονόμησης ενέργειας που μπορεί να μειώσει την κατανάλωση ενέργειας Macrocell κατά περισσότερο από 50%, γεγονός που είναι επωφελής για ενεργειακά αποδοτικές εφαρμογές.

Υποστήριξη δοκιμής JTAG Boundary-Scan : Συσκευές με 128 ή περισσότερα μακροκύτταρα, όπως αυτή, περιλαμβάνουν χαρακτηριστικά δοκιμών πλήρους οριακής σάρωσης για αποτελεσματική διάγνωση και επικύρωση σε επίπεδο σκάφους.

Bit Security για προστασία σχεδιασμού: Ένα προγραμματιζόμενο bit ασφαλείας εξασφαλίζει ότι ο εσωτερικός σχεδιασμός δεν μπορεί να διαβαστεί ή να αντιγραφεί, προστατεύοντας την πνευματική ιδιοκτησία.

Συμβατά με PCI I/O: Η δομή εισόδου/εξόδου έχει σχεδιαστεί για να πληροί τις ηλεκτρικές απαιτήσεις PCI, επιτρέποντας την άμεση διασύνδεση με συστήματα που βασίζονται σε PCI.

Εύρος θερμοκρασίας λειτουργίας 0 ° C έως 70 ° C: Η τυπική περιοχή θερμοκρασίας εμπορικής ποιότητας καθιστά αυτή τη συσκευή κατάλληλη για τις περισσότερες εφαρμογές εσωτερικού και ελεγχόμενου περιβάλλοντος.

EPM7192SQC160-15 Διάγραμμα pinout

Αυτό το διάγραμμα δείχνει τη διάταξη PIN για το EPM7192SQC160-15 και παρόμοιες συσκευές altera max 7000S.Το τσιπ έχει 160 καρφίτσες διατεταγμένες γύρω από τις τέσσερις πλευρές σε ένα τετράγωνο πακέτο QFP.Ο ακροδέκτης 1 ξεκινά από τη γωνία προς τα πάνω αριστερά και οι αριθμοί πηγαίνουν αριστερόστροφα γύρω από το τσιπ.Κάθε πλευρά έχει 40 καρφίτσες.Η μικρή κουκκίδα στην κορυφαία ακρίβεια σημείων 1, που βοηθά με την κατάλληλη τοποθέτηση.Το όνομα τσιπ στο κέντρο δείχνει ότι είναι συμβατό με άλλα μοντέλα στην ίδια οικογένεια.Αυτή η διάταξη παρέχει πολλές συνδέσεις εισόδου/εξόδου και είναι χρήσιμη για σύνθετα λογικά σχέδια.

Διάγραμμα μπλοκ Max 7000s

Αυτό το διάγραμμα μπλοκ δείχνει την εσωτερική δομή του CPLD Max 7000S, συμπεριλαμβανομένου του EPM7192SQC160-15.Το τσιπ χωρίζεται σε τέσσερα κύρια τμήματα που ονομάζονται μπλοκ λογικής συστοιχίας (Lab A έως D).Κάθε εργαστήριο διαθέτει 16 μακροκύτταρα, τα οποία είναι μικρές λογικές μονάδες που χρησιμοποιούνται για την κατασκευή ψηφιακών κυκλωμάτων.Μαζί, αυτά τα εργαστήρια χειρίζονται σύνθετες λογικές λειτουργίες.

Στο κέντρο υπάρχει η προγραμματιζόμενη συστοιχία διασύνδεσης (PIA), η οποία συνδέει όλα τα εργαστήρια και τους επιτρέπει να μοιράζονται δεδομένα.Κάθε εργαστήριο στέλνει και λαμβάνει σήματα μέσω 36 καναλιών, δίνοντας ευέλικτη δρομολόγηση μεταξύ λογικών μπλοκ.Γύρω από τις άκρες, υπάρχουν μπλοκ ελέγχου I/O που συνδέουν 6 με 16 ακίδες I/O σε κάθε εργαστήριο, επιτρέποντας στη συσκευή να συνδεθεί με άλλα μέρη ενός συστήματος.

Στην κορυφή, εμφανίζονται παγκόσμια σήματα ελέγχου όπως τα ρολόγια και η έξοδος.Αυτά τα σήματα συμβάλλουν στη διαχείριση του τρόπου με τον οποίο τα δεδομένα κινούνται μέσα στο τσιπ και όταν είναι ενεργές οι εξόδους.Συνολικά, το διάγραμμα δείχνει πώς το EPM7192SQC160-15 οργανώνει τη λογική και τις συνδέσεις του για να υποστηρίξει προσαρμοσμένα ψηφιακά σχέδια.

EPM7192SQC160-15 Προδιαγραφές

|

Τύπος |

Παράμετρος |

|

Κατασκευαστής |

Άλλος |

|

Σειρά |

MAX® 7000S |

|

Συσκευασία |

Δίσκος |

|

Κατάσταση μέρους |

Απηρχαιωμένος |

|

Προγραμματιζόμενος τύπος |

Σε προγραμματιζόμενο σύστημα |

|

Χρόνος καθυστέρησης TPD (1) Max |

15 ns |

|

Προμήθεια τάσης - Εσωτερική |

4.75V ~ 5.25V |

|

Αριθμός λογικών στοιχείων/μπλοκ |

12 |

|

Αριθμός μακροκύρων |

192 |

|

Αριθμός πύλων |

3750 |

|

Αριθμός I/O |

124 |

|

Θερμοκρασία λειτουργίας |

0 ° C ~ 70 ° C (ΤΑ) |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Πακέτο / θήκη |

160-BQFP |

|

Πακέτο συσκευών προμηθευτή |

160-PQFP (28x28) |

|

Αριθμός προϊόντος βάσης |

EPM7192 |

EPM7192SQC160-15 Εφαρμογές

Ενσωματωμένο λογικό κόλλας συστήματος

Το EPM7192SQC160-15 είναι ιδανικό για τη γεφύρωση διαφορετικών ψηφιακών συσκευών σε ενσωματωμένα συστήματα.Μπορεί να χρησιμοποιηθεί για τη διαχείριση της επικοινωνίας μεταξύ των μικροελεγκτών, των τσιπ μνήμης και των συσκευών I/O με τη διαχείριση της αποκωδικοποίησης διευθύνσεων, του ελέγχου των λεωφορείων και των ρυθμίσεων χρονισμού χωρίς να χρειάζονται διακριτές λογικές.

Κρατικές μηχανές και λογική ελέγχου

Με τα 192 μακροκύτταρα, το τσιπ είναι κατάλληλο για την εφαρμογή μηχανών προσαρμοσμένης κατάστασης και τη λογική ελέγχου.Χρησιμοποιείται συνήθως σε εργασίες αυτοματισμού, ελεγκτές κινητήρα και συστήματα ελέγχου που βασίζονται σε χρονισμό που απαιτούν αξιόπιστες και επαναλαμβανόμενες μεταβάσεις κατάστασης.

Διεπαφές πρωτοκόλλου επικοινωνίας

Αυτό το CPLD μπορεί να προγραμματιστεί για να δημιουργήσει ή να μεταφραστεί πρωτόκολλα επικοινωνίας όπως UART, SPI, I²C ή προσαρμοσμένες σειριακές μορφές.Επιτρέπει την εύκολη διαμόρφωση και τροποποίηση χωρίς να αλλάζει υλικό, καθιστώντας το πολύτιμο για τη διεπαφή επικοινωνίας.

Ψηφιακή προεπεξεργασία ψηφιακού σήματος

Χάρη στην ταχύτητα γρήγορης λογικής και την καθυστέρηση χαμηλής διάδοσης, μπορεί να χειριστεί απλές εργασίες επεξεργασίας σήματος, όπως φιλτράρισμα, πολυπλεξία ή ανίχνευση ακμής πριν τα σήματα φθάσουν στον κύριο επεξεργαστή ή το τσιπ DSP.

Μετάφραση διασύνδεσης και μετατόπιση επιπέδων

Η δυνατότητα I/O του Multivolt υποστηρίζει τόσο σήματα 3.3V και 5V.Αυτό το καθιστά κατάλληλο για σχέδια που περιλαμβάνουν εξαρτήματα που λειτουργούν σε διαφορετικά επίπεδα τάσης, επιτρέποντας την ασφαλή και αποτελεσματική μετάφραση τάσης.

Ταχεία ενημερώσεις πρωτότυπων και στο σύστημα

Μπορείτε να χρησιμοποιήσετε αυτό το τσιπ σε συστήματα που μπορεί να απαιτούν συχνές ενημερώσεις λογικής.Η δομή που βασίζεται στο EEPROM και η διεπαφή προγραμματισμού JTAG καθιστούν δυνατή την επανεγκατάσταση της λογικής ακόμη και μετά τη συναρμολόγηση του πίνακα.

Δοκιμή και διάγνωση σε επίπεδο συμβουλίου

Με την υποστήριξη των ορίων-σάρωσης μέσω JTAG, δοκιμάστε τις συνδέσεις μεταξύ των τσιπ σε PCB χωρίς να χρειάζεστε ανιχνευτές.Αυτό είναι χρήσιμο κατά τη διάρκεια της παραγωγής και του διαγνωστικού εντός πεδίου για την ανίχνευση θεμάτων συγκόλλησης ή δρομολόγησης.

EPM7192SQC160-15 Παρόμοια μέρη

• EPM7192EQC160-20 (Altera)

Αυτή η συσκευή είναι από την ίδια σειρά Max 7000 και προσφέρει τους ίδιους λογικούς πόρους, 192 μακροκύτταρα και 124 ακίδες I/O σε ένα πακέτο PQFP 160 PIN.Λειτουργεί σε βραδύτερη ταχύτητα -20, που σημαίνει ότι έχει μεγαλύτερες καθυστερήσεις διάδοσης (~ 20 ns), αλλά εξακολουθεί να ανταποκρίνεται στις ανάγκες των μη κρίσιμων σχεδίων.Είναι μια κατάλληλη εναλλακτική λύση για εφαρμογές όπου η λογική πυκνότητα είναι σημαντική, αλλά η εξαιρετικά γρήγορη χρονική στιγμή δεν αποτελεί προτεραιότητα, καθιστώντας το ιδανικό για ευαίσθητα σε κόστος έργα που εξακολουθούν να χρειάζονται λειτουργική ισοδυναμία.

• EPM7192SQI160-10N (Altera)

Αυτό το μέρος είναι επίσης συμβατό με τη λογική με το EPM7192SQC160-15, προσφέροντας τον ίδιο αριθμό μακροκύρων και I/OS.Ωστόσο, χρησιμοποιεί βαθμό ταχύτητας -10, η οποία υποστηρίζει ταχύτερη λειτουργία με βελτιωμένο χρονισμό (καθυστέρηση διάδοσης 10 NS).Υποστηρίζει επίσης ένα εκτεταμένο εύρος θερμοκρασίας από -40 ° C έως +85 ° C, καθιστώντας το εξαιρετικό υποκατάστατο των βιομηχανικών ή υπαίθριων εφαρμογών.Αυτό το καθιστά ιδανικό όταν απαιτούνται υψηλότερη ταχύτητα και περιβαλλοντική ανθεκτικότητα.

• EPM7192SQC160-7 (Intel)

Ως παραλλαγή άμεσης επιτάχυνσης του EPM7192SQC160-15, η έκδοση -7 παρέχει την ταχύτερη απόδοση στην οικογένεια, με τη διάδοση να καθυστερεί σε 7,5 ns.Διατηρεί την ίδια διαμόρφωση PIN, προδιαγραφές ισχύος και λογική πυκνότητα, προσφέροντας αντικατάσταση drop-in για όσους αναζητούν καλύτερη ταχύτητα χωρίς να μεταβάλλουν τις απαιτήσεις διάταξης ή τάσης.Αυτό το καθιστά την καλύτερη επιλογή για σχέδια κρίσιμης σημασίας για το χρόνο που χρειάζονται ταχύτερη απόκριση σήματος ενώ παραμένουν εντός του ίδιου αποτυπώματος σχεδιασμού.

EPM7192SQC160-15 Βήματα προγραμματισμού

1. Εισαγάγετε τη λειτουργία ISP

Το πρώτο βήμα είναι η μετατόπιση της συσκευής σε λειτουργία ISP (προγραμματισμός στο σύστημα).Αυτό γίνεται μέσω της διεπαφής JTAG.Μόλις βρεθεί σε λειτουργία ISP, όλες οι ακροδέκτες I/O στη συσκευή τοποθετούνται σε μια ασφαλή λειτουργία Tri-State για να αποφευχθεί η ακούσια λογική παρεμβολή κατά τον προγραμματισμό.Αυτή η αρχικοποίηση συνήθως διαρκεί περίπου 1 χιλιοστό του δευτερολέπτου.

2. Ελέγξτε το αναγνωριστικό συσκευής

Ένα μοναδικό αναγνωριστικό πυριτίου είναι ενσωματωμένο στη συσκευή για να επαληθεύσει ότι είναι το σωστό μοντέλο πριν αρχίσει ο προγραμματισμός.Το σύστημα μετατοπίζεται σε μια εντολή ανάγνωσης και ανακτά το αναγνωριστικό μέσω της γραμμής TDO (δοκιμών).Αυτός ο έλεγχος εξασφαλίζει ότι το εργαλείο προγραμματισμού συνδέεται με το σωστό CPLD και αποφεύγει λάθη όπως η αντικατάσταση ενός διαφορετικού μέρους.

3. Διαγραφή χύδην

Μια μαζική διαγραφή καθαρίζει όλα τα αποθηκευμένα δεδομένα που έχουν προηγουμένως αποθηκευτεί στη μνήμη EEPROM του CPLD.Αυτό προετοιμάζει το τσιπ για να λάβει μια νέα διαμόρφωση.Η εντολή διαγραφής ξεκινά έναν παλμό που συνήθως διαρκεί περίπου 100 χιλιοστά του δευτερολέπτου, εξασφαλίζοντας ότι όλα τα προγραμματιζόμενα κύτταρα επαναφέρονται.

4. Πρόγραμμα EEPROM

Τα νέα δεδομένα διαμόρφωσης φορτώνονται στη συσκευή μετατοπίζοντας τη διεύθυνση και τα bits δεδομένων μέσω της θύρας JTAG.Κάθε κελί μνήμης είναι γραμμένο ένα προς ένα, με παλμό προγραμματισμού που εφαρμόζεται μετά από κάθε επιτυχημένο κύκλο εγγραφής.Αυτή η διαδικασία καθορίζει τη λογική δομή που θα χρησιμοποιήσει το CPLD όταν τροφοδοτείται.

5. Επαληθεύστε το EEPROM

Μετά τον προγραμματισμό, η συσκευή εκτελεί ένα βήμα επαλήθευσης.Αυτό περιλαμβάνει την ανάγνωση κάθε τοποθεσίας μνήμης προγραμματισμένης μνήμης και τη σύγκριση των τιμών εξόδου με τα προβλεπόμενα δεδομένα.Εάν η επαλήθευση αποτύχει, η διαδικασία πρέπει να επαναληφθεί.Αυτό το βήμα εγγυάται ότι η διαμόρφωση γράφτηκε με επιτυχία.

6. Λειτουργία εξόδου ISP

Μόλις ολοκληρωθεί η επαλήθευση, εκδίδεται τελική εντολή για την έξοδο του ISP.Η συσκευή επανενεργοποιεί τις ακίδες I/O και επαναλαμβάνει την κανονική λειτουργία.Αυτή η μετάβαση διαρκεί επίσης περίπου 1 χιλιοστό του δευτερολέπτου και ολοκληρώνει τον κύκλο προγραμματισμού στο σύστημα.

EPM7192SQC160-15 Διαστάσεις συσκευασίας

• Μέγεθος σώματος: 28mm × 28mm

• Ύψος πακέτου: 3,4 χιλιοστά

• Πηνίο: 0,65 χιλιοστά

EPM7192SQC160-15 Κατασκευαστής

Το EPM7192SQC160-15 κατασκευάστηκε αρχικά από Altera Corporation, μια εταιρεία γνωστή για τις προηγμένες προγραμματιζόμενες λογικές συσκευές της.Το 2015, η Altera αποκτήθηκε από Εταιρία Intel, και η συσκευή είναι τώρα μέρος της ομάδας προγραμματιζόμενων λύσεων της Intel υπό την οικογένεια CPLD Max 7000S.Η Intel συνεχίζει να υποστηρίζει τα προϊόντα Legacy Altera, αν και το EPM7192SQC160-15 ταξινομείται τώρα ως παρωχημένη στους περισσότερους επίσημους καταλόγους.Παρά την διακοπή της κατάστασης, η ιστορική φήμη της Intel για την αξιοπιστία και την κληρονομιά της Altera στις λύσεις λογικής υψηλής απόδοσης εξασφαλίζουν τη συνεχιζόμενη ζήτηση και τη διαθεσιμότητα μέσω δευτερογενών διανομέων.

Σύναψη

Το EPM7192SQC160-15 είναι ένα χρήσιμο και εύκαμπτο τσιπ για τη διαχείριση εργασιών ψηφιακού ελέγχου σε πολλά ηλεκτρονικά συστήματα.Προσφέρει αρκετή λογική ισχύ για θέσεις εργασίας όπως η κατασκευή προσαρμοσμένων μηχανών, τα σήματα χειρισμού και η σύνδεση διαφορετικών συσκευών.Υποστηρίζει διαφορετικά επίπεδα τάσης, λειτουργεί με γρήγορες ταχύτητες και μπορεί να ενημερωθεί εύκολα μέσω του JTAG.Ο εσωτερικός του σχεδιασμός επιτρέπει την ομαλή ροή σήματος και τις εύκολες λογικές αλλαγές.Παρόλο που τώρα διακόπτεται, εξακολουθεί να είναι μια εξαιρετική επιλογή για παλιά ή συνεχιζόμενα έργα και μπορεί να αντικατασταθεί με παρόμοιες μάρκες που προσφέρουν ταχύτερη ή ευρύτερη υποστήριξη θερμοκρασίας.

Φύλλο δεδομένων PDF

EPM7192SQC160-15 φύλλα δεδομένων:

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Συχνές ερωτήσεις [FAQ]

1. Μπορώ να προγραμματίσω το EPM7192SQC160-15 χωρίς να το αφαιρέσω από την πλακέτα κυκλώματος;

Ναι, το Chip υποστηρίζει τον προγραμματισμό στο σύστημα (ISP) μέσω της διασύνδεσης JTAG, ώστε να μπορείτε να προγραμματίσετε ή να το επαναπρογραμματίσετε απευθείας ενώ είναι συγκολλημένη στο PCB, το οποίο απλοποιεί τις ενημερώσεις σχεδιασμού και μειώνει την επανεξέταση.

2. Ποιο λογισμικό προγραμματισμού πρέπει να χρησιμοποιήσω για το EPM7192SQC160-15;

Μπορείτε να χρησιμοποιήσετε το λογισμικό Quartus II της Altera (παλαιότερες εκδόσεις) για να δημιουργήσετε λογικά σχέδια, να συντάξετε τον κώδικα και να διαχειριστείτε τη διαδικασία προγραμματισμού που βασίζεται στην JTAG.Το Quartus II υποστηρίζει συσκευές Max 7000S όπως το EPM7192SQC160-15.

3. Το EPM7192SQC160-15 απαιτεί εξωτερική μνήμη για λειτουργία;

Όχι, έχει εσωτερική μνήμη διαμόρφωσης με βάση το EEPROM.Όλες οι διαμόρφωσης λογικής αποθηκεύονται μέσα στο τσιπ, οπότε δεν απαιτείται εξωτερική μνήμη για την αποθήκευση των καταστάσεων λογικής ή των ακολουθιών εκκίνησης.

4. Τι κάνει το EPM7192SQC160-15 κατάλληλο για βιομηχανική χρήση;

Η ισχυρή λειτουργία του 5V, η συμβατότητα με I/O πολλαπλών I/O, η γρήγορη λογική επεξεργασία και η μη πτητική μνήμη που βασίζεται σε EEPROM καθιστούν αξιόπιστη για βιομηχανικά συστήματα που απαιτούν σταθερές και ανθεκτικές ψηφιακές λογικές λειτουργίες.

5. Πώς το EPM7192SQC160-15 χειρίζεται συστήματα μικτής τάσης;

Χάρη στη στήριξη πολλαπλών I/O του Multivolt, η συσκευή μπορεί να διασυνδέεται με τα επίπεδα λογικής 3,3V και 5V, καθιστώντας την ιδανική για συστήματα μικτού σήματος και διασύνδεση με σύγχρονα εξαρτήματα χαμηλής τάσης.

Γιατί να επιλέξετε το EPF10K100EFC484-3 για το έργο σας

στο 2025/06/13

Τι είναι ο διακόπτης SPST και πώς λειτουργεί;

στο 2025/06/12

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/18 147760

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/18 111974

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/18 111351

-

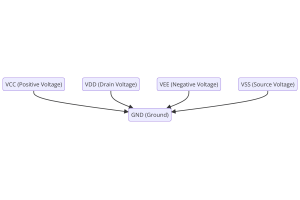

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/18 83742

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79527

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66937

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63086

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63025

-

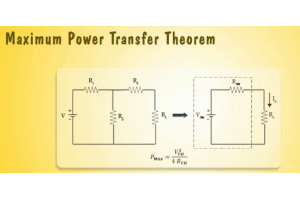

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54092

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52167