EP1C4F400C8 FPGA: Χαρακτηριστικά, προδιαγραφές, προγραμματισμός και εναλλακτικές λύσεις

Εάν εργάζεστε με προγραμματιζόμενη λογική, το EP1C4F400C8 σας δίνει μια πρακτική ισορροπία απόδοσης και κόστους.Σε αυτό το άρθρο, θα μάθετε τι είναι αυτό το FPGA, τα βασικά χαρακτηριστικά του όπως η λογική χωρητικότητα, η μνήμη και οι επιλογές I/O και πώς η δομή του υποστηρίζει αξιόπιστο σχεδιασμό.Θα δείτε επίσης τις προδιαγραφές, τις εφαρμογές σε συστήματα, τη διαδικασία προγραμματισμού και τον τρόπο με τον οποίο συγκρίνεται με παρόμοια μέρη.Κατάλογος

Ποιο είναι το EP1C4F400C8;

Ο EP1C4F400C8 είναι μέλος της οικογένειας FPGA της Intel (πρώην Altera's), σχεδιασμένη ως οικονομικά αποδοτική και αξιόπιστη προγραμματιζόμενη λογική λύση.Χτισμένο σε μια διαδικασία SRAM 0,13 μm, αυτή η συσκευή προσφέρει μέτρια λογική πυκνότητα και ευέλικτες επιλογές I/O μέσα σε ένα συμπαγές πακέτο FBGA-400.Η οικογένεια Cyclone, η οποία περιλαμβάνει συσκευές όπως EP1C3, EP1C6, EP1C12 και EP1C20, δημιουργήθηκε για να εξισορροπήσει την απόδοση και την οικονομική προσιτότητα για κλιμακούμενα σχέδια, επιτρέποντας εύκολη μετανάστευση μεταξύ επιπέδων πυκνότητας και πακέτων.Γνωστή για τη σταθερότητα και την ευρεία υιοθέτηση, παραμένει μια αξιόπιστη επιλογή στα σχέδια κληρονομιάς.

Ψάχνετε για EP1C4F400C8;Επικοινωνήστε μαζί μας για να ελέγξετε το τρέχον απόθεμα, το χρόνο παράδοσης και την τιμολόγηση.

EP1C4F400C8 CAD μοντέλα

Σύμβολο EP1C4F400C8

Αποτύπωμα EP1C4F400C8

EP1C4F400C8 3D μοντέλο

Χαρακτηριστικά EP1C4F400C8

• Λογική χωρητικότητα

Το EP1C4F400C8 προσφέρει περίπου 4.000 λογικά στοιχεία, που οργανώνονται σε 400 μπλοκ πίνακα λογικών (LABS).Αυτό το καθιστά κατάλληλο για σχέδια μεσαίας εμβέλειας που απαιτούν μέτρια λογική πυκνότητα διατηρώντας παράλληλα την απόδοση του κόστους.

• Ενσωματωμένη μνήμη

Ενσωματώνει περίπου 76,5 kbits ενσωματωμένης μνήμης.Αυτή η εσωτερική μνήμη RAM υποστηρίζει τις λειτουργίες buffering, αποθήκευσης και μικρής μνήμης, μειώνοντας την ανάγκη για εξωτερικά εξαρτήματα μνήμης σε πολλά σχέδια.

• Υψηλή είσοδος/εξόδου

Η συσκευή παρέχει 301 ακροδέκτες I/O που μπορούν να διαμορφωθούν από το χρήστη στο πακέτο FBGA 400 Ball.Αυτός ο υψηλός αριθμός ακίδων επιτρέπει την πλούσια συνδεσιμότητα για σύνθετα συστήματα που απαιτούν πολλαπλές περιφερειακές διεπαφές.

• Υποστήριξη προτύπων ευρείας εισόδου/εξόδου

Υποστηρίζει πολλαπλά πρότυπα εισόδου/εξόδου, όπως LVTTL, LVCMOS, SSTL-2, SSTL-3 και διαφορικά LVD.Αυτή η ευελιξία επιτρέπει στο FPGA να διασυνδέεται απευθείας με μια ποικιλία από σύγχρονες λογικές οικογένειες και συσκευές μνήμης.

• Διαφορική σηματοδότηση υψηλής ταχύτητας

Με την υποστήριξη LVDS έως και 640 Mbps, το FPGA χειρίζεται γρήγορες απαιτήσεις μεταφοράς δεδομένων.Αυτό το καθιστά πρακτικό για εφαρμογές, όπως συνδέσεις επικοινωνίας υψηλής ταχύτητας και γρήγορες ψηφιακές διεπαφές.

• Διαχείριση ρολογιού με PLLS

Το τσιπ ενσωματώνει δύο βρόχους φάσης (PLLS) και οκτώ παγκόσμια δίκτυα ρολογιών.Αυτά τα χαρακτηριστικά επιτρέπουν την ακριβή παραγωγή ρολογιού, τον πολλαπλασιασμό και τον έλεγχο jitter για εφαρμογές κρίσιμης σημασίας για το χρονισμό.

• Λειτουργία πυρήνα χαμηλής τάσης

Λειτουργώντας σε ονομαστική τάση πυρήνα 1,5 V, η συσκευή εξισορροπεί την απόδοση με χαμηλότερη κατανάλωση ενέργειας.Αυτό το επίπεδο τάσης βελτιστοποιήθηκε για την τεχνολογία CMOS 0,13 μm που χρησιμοποιήθηκε στην κατασκευή της.

• Ευέλικτες τάσεις εισόδου/εξόδου

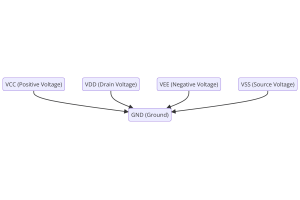

Το FPGA υποστηρίζει τάσεις I/O 1,5 V, 1,8 V, 2,5 V και 3,3 V σε διαφορετικές τράπεζες.Αυτή η ευελιξία της επιτρέπει να διασυνδέεται τόσο με την κληρονομιά όσο και με τα σύγχρονα συστατικά του συστήματος.

• Διαμόρφωση βασισμένη σε SRAM

Όπως και άλλοι Cyclone FPGAs, βασίζεται σε SRAM και απαιτεί αναδιαμόρφωση σε κάθε power-up.Αυτό παρέχει ευελιξία για ενημερώσεις, αλλά απαιτεί επίσης μια εξωτερική συσκευή διαμόρφωσης ή ελεγκτή.

• Υποστήριξη συμπίεσης bitstream

Το EP1C4F400C8 υποστηρίζει τη συμπιεσμένη φόρτιση bitstream κατά τη διάρκεια της διαμόρφωσης.Αυτό μειώνει τις απαιτήσεις εξωτερικής μνήμης και επιταχύνει τους χρόνους διαμόρφωσης.

• Συμμόρφωση με PCI

Περιλαμβάνει ενσωματωμένη υποστήριξη για πρότυπα PCI (33/66 MHz, 32/64-bit).Αυτή η λειτουργία επιτρέπει στη συσκευή να ενσωματωθεί άμεσα σε συστήματα που απαιτούν διασύνδεση PCI χωρίς πρόσθετη λογική γεφύρωσης.

Δομή εργαστηρίου κυκλώνα

Το διάγραμμα εμφανίζει τη δομή μπλοκ λογικής (LAB) που χρησιμοποιείται σε Cyclone FPGAs όπως το EP1C4F400C8.Κάθε εργαστήριο συνδέεται με ένα δίκτυο διασύνδεσης: διασυνδέσεις γραμμών, διασυνδέσεις στήλης και τοπικές διασυνδέσεις, τα οποία σήματα διαδρομής μεταξύ λογικών στοιχείων και άλλων μπλοκ.Οι διασυνδέσεις άμεσης σύνδεσης παρέχουν γρήγορες διαδρομές χαμηλής καθυστέρησης σε γειτονικά εργαστήρια, βελτιώνοντας την απόδοση του χρονισμού στις διαδρομές σήματος.Αυτή η αρχιτεκτονική είναι σημαντική επειδή ισορροπεί τη δρομολόγηση της ευελιξίας με την αποτελεσματικότητα, επιτρέποντας στο FPGA να χειρίζεται σύνθετα σχέδια, διατηρώντας παράλληλα την ταχύτητα και την περιοχή βελτιστοποιημένη.

Cyclone I/O Banks Diagram

Το διάγραμμα απεικονίζει τη δομή της τράπεζας I/O των Cyclone FPGAs όπως το EP1C4F400C8.Η συσκευή χωρίζεται σε τέσσερις τράπεζες εισόδου/εξόδου, καθένα από τα οποία τροφοδοτείται από το δικό της δίαυλο τροφοδοσίας, επιτρέποντας να αναμειγνύεται διαφορετικά πρότυπα τάσης μέσα σε ένα μόνο FPGA.Όλες οι τράπεζες υποστηρίζουν ένα ευρύ φάσμα προτύπων εισόδου/εξόδου, όπως LVTTL, LVCMOS, LVDS, RSDS και SSTL, ενώ οι τράπεζες 1 και 3 υποστηρίζουν επίσης 3.3-V PCI για συμβατότητα με τα κληροδοτημένα συστήματα.Αυτή η ευέλικτη αρχιτεκτονική I/O είναι σημαντική επειδή επιτρέπει την απρόσκοπτη ενσωμάτωση με διάφορες εξωτερικές συσκευές και διεπαφές, καθιστώντας το FPGA προσαρμόσιμο σε διάφορες εφαρμογές.

Προδιαγραφές EP1C4F400C8

|

Τύπος |

Παράμετρος |

|

Κατασκευαστής |

Altera/intel |

|

Σειρά |

Cyclone® |

|

Συσκευασία |

Δίσκος |

|

Κατάσταση μέρους |

Απηρχαιωμένος |

|

Αριθμός εργαστηρίων/CLB |

400 |

|

Αριθμός λογικών στοιχείων/κυττάρων |

4000 |

|

Συνολικά κομμάτια μνήμης RAM |

78,336 |

|

Αριθμός I/O |

301 |

|

Τάση - προμήθεια |

1.425V ~ 1.575V |

|

Τύπος τοποθέτησης |

Επιφανειακή βάση |

|

Θερμοκρασία λειτουργίας |

0 ° C ~ 85 ° C (TJ) |

|

Πακέτο / θήκη |

400-BGA |

|

Πακέτο συσκευών προμηθευτή |

400-FBGA (21 × 21) |

|

Αριθμός προϊόντος βάσης |

EP1C4 |

Εφαρμογές EP1C4F400C8

1. Επεξεργασία ψηφιακού σήματος (DSP)

Το EP1C4F400C8 μπορεί να προγραμματιστεί για να εκτελέσει εργασίες όπως φιλτράρισμα, FFTS και διαμόρφωση σήματος.Ο συνδυασμός λογικών στοιχείων και ενσωματωμένης μνήμης το καθιστά κατάλληλο για επεξεργασία υψηλής ταχύτητας.Αυτό του επιτρέπει να αντικαταστήσει τα παραδοσιακά τσιπ DSP με μια εύκαμπτη λύση FPGA που μπορεί να επαναπρογραμματιστεί για διαφορετικούς αλγόριθμους.

2. Ενσωματωμένα και συστήματα ελέγχου

Στα βιομηχανικά και ενσωματωμένα συστήματα, αυτό το FPGA χρησιμοποιείται συχνά για την εφαρμογή προσαρμοσμένων ελεγκτών, αλληλουχιών και μηχανών κατάστασης.Η αναδιαμορφώσιμη λογική της επιτρέπει την προσαρμογή της συμπεριφοράς υλικού ακριβώς στις ανάγκες του συστήματος.Με την ενσωμάτωση της λογικής ελέγχου μέσα στο FPGA, ο αριθμός των εξωτερικών εξαρτημάτων μειώνεται, βελτιώνοντας την αξιοπιστία και το κόστος μείωσης.

3. Γεφύρωση επικοινωνίας και διασύνδεσης

Η συσκευή υποστηρίζει πολλαπλά πρότυπα εισόδου/εξόδου και μπορεί να λειτουργήσει ως γέφυρα μεταξύ διαφορετικών πρωτοκόλλων επικοινωνίας.Συχνά χρησιμοποιείται για τη σύνδεση PCI, LVD, SDRAM και άλλες διεπαφές απρόσκοπτα μέσα σε ένα σύστημα.Αυτό το καθιστά εξαιρετικά χρήσιμο στον εξοπλισμό δικτύωσης, τους ενσωματωμένους ελεγκτές και τις μετατροπές κληρονομιάς σε μοντέρνα διασύνδεσης.

4. Λήψη και επεξεργασία δεδομένων

Με υψηλή διαθεσιμότητα I/O και ευέλικτη μνήμη, το EP1C4F400C8 είναι κατάλληλο για συστήματα συλλογής δεδομένων.Μπορεί να διασυνδέεται άμεσα με ADC και αισθητήρες, να επεξεργαστεί τα δεδομένα εγκαίρως και να τα προετοιμάσει για αποθήκευση ή μετάδοση.Τέτοιες εφαρμογές είναι κοινές σε ιατρικά μέσα, εξοπλισμό δοκιμών και συσκευές επιστημονικής μέτρησης.

EP1C4F400C8 Παρόμοια μέρη

|

Προσδιορισμός |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Κατασκευαστής |

Altera (intel) |

Altera (intel) |

Altera (intel) |

Altera (intel) |

Altera (intel) |

Altera (intel) |

|

Οικογένεια FPGA |

Κυκλώνας (EP1C4) |

Κυκλώνας (EP1C4) |

Κυκλώνας (EP1C4) |

Κυκλώνας (EP1C4) |

Κυκλώνας (EP1C4) |

Κυκλώνας (EP1C4) |

|

Λογικά στοιχεία (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Ενσωματωμένη μνήμη (bits) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O καρφίτσες |

301 |

301 |

301 |

301 |

249 |

97 |

|

Πακέτο / θήκη |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Βαθμός ταχύτητας |

C8 |

C8 |

C8 |

C6 (γρηγορότερα) |

C8 |

C8 |

|

Τάση πυρήνα |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

|

Λειτουργική θερμοκρασία.Σειρά |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 Βήματα προγραμματισμού

Πριν μπορέσετε να χρησιμοποιήσετε το EP1C4F400C8 FPGA, πρέπει να φορτώσετε το σχέδιό σας στη συσκευή.Ο προγραμματισμός περιλαμβάνει τη διαμόρφωση του FPGA με ένα αρχείο bitstream, ώστε να ξέρει πώς να συμπεριφέρεται ως το προβλεπόμενο κύκλωμα σας.

1. Επιλέξτε Σχέδιο διαμόρφωσης & Set MSEL PINS

Ξεκινάτε επιλέγοντας το σχήμα διαμόρφωσης που ταιριάζει καλύτερα στη ρύθμισή σας, όπως ενεργό σειριακό, παθητικό σειριακό ή JTAG.Αυτό γίνεται με τη ρύθμιση των ακίδων MSEL σε συγκεκριμένα επίπεδα λογικής πριν από την ενεργοποίηση.Κάθε λειτουργία χρησιμοποιεί διαφορετικές ακίδες και πρωτόκολλα, οπότε πρέπει να επιβεβαιώσετε τη συμβατότητα με τα εργαλεία σχεδιασμού και τη μνήμη διαμόρφωσης.Κάνοντας τη σωστή επιλογή εδώ εξασφαλίζει μια ομαλή διαδικασία διαμόρφωσης.

2. Εφαρμόστε ισχύ και αρχικοποιήστε τη συσκευή

Στη συνέχεια, ενεργοποιήστε τον πυρήνα του FPGA και τις ράγες I/O εντός των καθορισμένων περιοχών τάσης.Κατά τη διάρκεια της εκκίνησης, κρατήστε το PIN NCONFIG LOW για να κρατήσετε τη συσκευή σε επαναφορά έως ότου οι τάσεις τροφοδοσίας είναι σταθερές.Μόλις σταθεροποιηθεί, απελευθερώνετε την επαναφορά και η συσκευή σηματοδοτεί την ετοιμότητα οδηγώντας την καρφίτσα NSTATUS.Αυτό εγγυάται ότι το FPGA έχει αρχικοποιηθεί σωστά πριν ξεκινήσει η διαμόρφωση.

3. Μεταδώστε το bitstream διαμόρφωσης

Σε αυτό το στάδιο, στέλνετε το αρχείο δεδομένων διαμόρφωσης (bitstream) στο FPGA χρησιμοποιώντας το επιλεγμένο σας σχήμα.Σε ενεργό σειριακό ή παθητικό σειριακό τρόπο, το bitstream προέρχεται από μια εξωτερική συσκευή μνήμης, ενώ το JTAG επιτρέπει άμεσο προγραμματισμό μέσω καλωδίου.Η συσκευή διαβάζεται συνεχώς στα δεδομένα διαμόρφωσης μέχρι να ολοκληρωθεί.Το λογισμικό σχεδιασμού σας δημιουργεί αυτό το bitstream για να ταιριάζει με τις απαιτήσεις λογικής σας.

4. Επιβεβαιώστε την επιτυχή διαμόρφωση (conf_done)

Όταν το FPGA ολοκληρώσει τη φόρτωση, ισχυρίζεται την PIN CONF_DONE για να δείξει ότι τα δεδομένα διαμόρφωσης ελήφθησαν με επιτυχία.Ταυτόχρονα, η συσκευή εκτελεί εσωτερική αρχικοποίηση, όπως καταχωρητές εκκαθάρισης και ενεργοποίηση I/O.Εάν το conf_done αποτύχει να φτάσει ψηλά, σημαίνει συνήθως ότι τα δεδομένα ή η ρύθμιση διαμόρφωσης έχει σφάλμα.Η παρακολούθηση αυτού του πείρου είναι ο απλούστερος τρόπος για να επαληθεύσετε τη διαδικασία είναι πλήρης.

5. Εκτελέστε προαιρετική αναδιάρθρωση στο σύστημα

Τέλος, έχετε την επιλογή να ενημερώσετε ή να επαναπρογραμματίσετε το FPGA χωρίς να το αφαιρέσετε από το διοικητικό συμβούλιο.Χρησιμοποιώντας το JTAG ή έναν ενσωματωμένο ελεγκτή, μπορείτε να φορτώσετε ένα νέο bitstream απευθείας, το οποίο είναι χρήσιμο για ενημερώσεις υλικολογισμικού.Αυτή η ευελιξία σας επιτρέπει να τροποποιήσετε, να εντοπίσετε ή να αναβαθμίσετε το σύστημά σας ακόμη και μετά την ανάπτυξη.Εξασφαλίζει ότι ο σχεδιασμός σας με βάση το FPGA μπορεί να προσαρμοστεί με την πάροδο του χρόνου στις μεταβαλλόμενες απαιτήσεις.

EP1C4F400C8 Πλεονεκτήματα και μειονεκτήματα

Φόντα

• Χαρακτηριστική επιλογή για σχέδια μεσαίας εμβέλειας

• Υψηλή μέτρηση εισόδου/εξόδου σε σύγκριση με παρόμοιες συσκευές πυκνότητας

• Ευέλικτη τάση και πρότυπη υποστήριξη I/O

• Υποστηριζόμενη από ώριμα εργαλεία και τεκμηρίωση

• χαμηλότερη χρήση ισχύος από τις παλαιότερες γενιές FPGA

Μειονεκτήματα

• Παρωχημένη με περιορισμένη μακροπρόθεσμη διαθεσιμότητα

• Χαμηλότερη λογική και χωρητικότητα μνήμης έναντι σύγχρονων FPGAs

• βραδύτερη ταχύτητα λειτουργίας και απόδοση I/O

• Απαιτεί εξωτερική μνήμη για διαμόρφωση σε λειτουργία Power-Up

• Δεν διαθέτει προηγμένες λειτουργίες όπως μπλοκ DSP και πομποδέκτες υψηλής ταχύτητας

EP1C4F400C8 Διαστάσεις συσκευασίας

|

Τύπος |

Παράμετρος |

|

Τύπος πακέτου |

FBGA (συστοιχία πλέγματος μπάλας λεπτών-pitch) |

|

Καταμέτρηση με μπάλα |

400 |

|

Μπάλα (ε) |

1,0 mm (τυπικό για κυκλώνα EP1C4F400) |

|

Διάμετρος μπάλας (β) |

0,45 mm (ονομαστική) |

|

Μέγεθος πακέτου (D × E) |

21 mm × 21 mm |

|

Ύψος πακέτου (α) |

2.40 mm (μέγιστο) |

|

Πάχος υποστρώματος (Α2) |

~ 0,40 mm |

|

Πάχος καλούπι (A3) |

~ 1,90 mm |

|

Ύψος μπάλας (a1) |

0,25 mm (ονομαστική) |

|

Pin A1 Corner |

Επισημάνθηκε για προσανατολισμό |

|

Διάταξη διαφορών |

20 × 20 πλέγμα (με γωνιακές μπάλες που λείπουν) |

|

Βάση |

Βάση επιφάνειας (SMD) |

Κατασκευαστής EP1C4F400C8

Το EP1C4F400C8 κατασκευάστηκε αρχικά από Altera Corporation, πρωτοπόρος σε προγραμματιζόμενες λογικές συσκευές και τεχνολογία FPGA.Το 2015, η Altera αποκτήθηκε από Εταιρία Intel, και η σειρά προϊόντων έγινε μέρος της ομάδας προγραμματιζόμενων λύσεων της Intel (PSG).Σήμερα, η Intel υποστηρίζει αυτές τις συσκευές Altera Altera, εστιάζοντας παράλληλα την ανάπτυξη στις νεότερες οικογένειες FPGA, εξασφαλίζοντας τη συνέχεια για τους υπάρχοντες χρήστες και προωθώντας την καινοτομία σε προγραμματιζόμενη λογική.

Σύναψη

Το EP1C4F400C8 ξεχωρίζει ως οικονομικά αποδοτικό και ευπροσάρμοστο FPGA που προσφέρει σταθερή απόδοση για σχέδια μεσαίας εμβέλειας.Με τα 4.000 λογικά στοιχεία, την ενσωματωμένη μνήμη, την εκτεταμένη υποστήριξη I/O και τη συμβατότητα με τα πρότυπα πολλαπλής τάσης και διασύνδεσης, παρέχει ευελιξία σε ποικίλες εφαρμογές.Η αρχιτεκτονική, η διαδικασία προγραμματισμού και η ευρεία χρηστικότητα σε DSP, ενσωματωμένα συστήματα και απόκτηση δεδομένων καθιστούν πρακτική επιλογή παρά την κληρονομιά της.Ενώ δεν διαθέτει προηγμένα χαρακτηριστικά που βρίσκονται σε νεότερες συσκευές και αντιμετωπίζει περιορισμένη μακροπρόθεσμη διαθεσιμότητα, παραμένει μια αξιόπιστη επιλογή που αναζητά αποδεδειγμένες λύσεις σε κλιμακούμενα σχέδια FPGA.

Φύλλο δεδομένων PDF

EP1C4F400C8 φύλλα δεδομένων:

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Συχνές ερωτήσεις [FAQ]

1. Ποια εργαλεία απαιτούνται για τον προγραμματισμό του EP1C4F400C8;

Χρειάζεστε λογισμικό Quartus της Intel (προηγουμένως altera quartus II) μαζί με ένα υποστηριζόμενο καλώδιο προγραμματισμού όπως το USB-blaster.Αυτά τα εργαλεία σας επιτρέπουν να δημιουργήσετε το bitstream και να το φορτώσετε στο FPGA.

2. Μπορεί το EP1C4F400C8 να χειριστεί απευθείας εφαρμογές PCI;

Ναι, έχει ενσωματωμένη συμμόρφωση για τα πρότυπα PCI (33/66 MHz, 32/64-bit), καθιστώντας την κατάλληλη για ενσωμάτωση συστήματος με βάση το PCI χωρίς να απαιτεί επιπλέον λογική γεφύρωσης.

3. Τι συμβαίνει εάν το EP1C4F400C8 αποτύχει κατά τη διάρκεια της διαμόρφωσης;

Εάν η διαμόρφωση αποτύχει, ο ακροδέκτης CONF_DONE δεν θα επιβεβαιώσει υψηλά.Αυτό συνήθως επισημαίνει ένα σφάλμα στο αρχείο bitstream, την αλληλουχία τάσης ή την ρύθμιση ακίδων και πρέπει να επανελέχονται στη ροή σχεδιασμού σας.

4 Μπορεί η EP1C4F400C8 να διασυνδέεται απευθείας με τη μνήμη DDR;

Υποστηρίζει διάφορα πρότυπα I/O, αλλά δεν διαθέτει εγγενείς διεπαφές DDR όπως τα σύγχρονα FPGAs.Μπορεί να χρειαστούν πρόσθετες εκτιμήσεις σχεδιασμού ή συστατικά γεφύρωσης.

5. Πώς συγκρίνεται το EP1C4F400C8 με νεότερα FPGAs;

Σε σύγκριση με τις σύγχρονες συσκευές, το EP1C4F400C8 έχει χαμηλότερη ταχύτητα, λιγότερη λογική πυκνότητα και λιγότερα προηγμένα χαρακτηριστικά.Ωστόσο, παραμένει μια οικονομικά αποδοτική επιλογή για σταθερά σχέδια μεσαίας εμβέλειας όπου δεν απαιτείται απόδοση αιχμής.

EPM3256AFC256-7 Επισκόπηση CPLD: Χαρακτηριστικά, pinout, προγραμματισμός και εφαρμογές

στο 2025/10/3

ADG432BR Αναλογικός διακόπτης IC: Προδιαγραφές, pinout, εναλλακτικές λύσεις και φύλλο δεδομένων

στο 2025/10/2

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/18 147772

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/18 112009

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/18 111351

-

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/18 83768

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79565

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66960

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63100

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63040

-

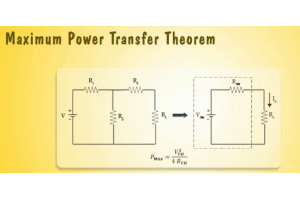

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54097

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52184