CPLD εξήγησε: Ένας οδηγός για προγραμματιζόμενες λογικές συσκευές

Στον δυναμικό κόσμο του ηλεκτρονικού σχεδιασμού, οι πολύπλοκες προγραμματιζόμενες λογικές συσκευές (CPLDs) ξεχωρίζουν ως ευπροσάρμοστα εργαλεία, αναμειγνύοντας απρόσκοπτα την προσαρμοστικότητα, την ακρίβεια και την αποτελεσματικότητα.Αυτές οι συσκευές επανάσταση στο σχεδιασμό κυκλωμάτων εισάγοντας προγραμματιζόμενα μακρο κύτταρα και κυρίαρχη μήτρα διασύνδεσης, επιτρέποντας τη δημιουργία περίπλοκων λογικών λειτουργιών με αξιοσημείωτη αξιοπιστία.Από την έναρξή τους στη δεκαετία του 1980 μέχρι τον βασικό τους ρόλο σε σύγχρονες βιομηχανίες όπως η δικτύωση, η αυτοκινητοβιομηχανία και η αεροδιαστημική, οι CPLD έχουν αποδειχθεί απαραίτητες για την αναζήτηση τόσο ευελιξίας όσο και απόδοσης.Αυτό το άρθρο εκσφενδονίζεται στο ταξίδι των CPLD, τα χαρακτηριστικά χαρακτηριστικά τους, τις πρακτικές εφαρμογές και τις μεθοδολογίες προγραμματισμού που τους καθιστούν ακρογωνιαίο λίθο σε σχεδιασμό ψηφιακής λογικής.Κατάλογος

Επισκόπηση του CPLD

Μέσα στην κυριαρχία σύνθετων προγραμματιζόμενων λογικών συσκευών (CPLDs), ανακαλύπτει μια εξελιγμένη ταπετσαρία προγραμματιζόμενων λογικών μακροκυττάρων, που συνυφαίνονται μέσω ενός κυρίαρχου μήτρας διασύνδεσης.Αυτές οι γραμμές μονάδων μακροεντολών (MC) και εισόδου/εξόδου (I/O) σας επιτρέπουν να σχεδιάζετε κυκλώματα σχεδιασμού, ρυθμίζοντας τις δομές για μοναδικές λειτουργίες.Σε αντίθεση με τις συσκευές που είναι αμηχανία από το περίπλοκο χρονισμό διασύνδεσης, τα CPLD χρησιμοποιούν ακίνητα μεταλλικά καλώδια.Αυτό το χαρακτηριστικό τους δίνει μια συνεπή και προβλέψιμη συμπεριφορά ρολογιού, καθιστώντας τις προβλέψεις χρονισμού πιο αξιόπιστες και ακριβείς.

Το ταξίδι και η αξιοποίηση

Η δεκαετία του 1970 προειδοποίησε την έλευση προγραμματιζόμενων λογικών συσκευών (PLDS), προωθώντας μια κίνηση προς προγραμματιζόμενες μακροοικονομικές μονάδες.Αυτή η μετατόπιση εισήγαγε άφθονη ευελιξία σχεδιασμού, τοποθετώντας τους εκτός από στατικά ψηφιακά κυκλώματα, αν και η χρησιμότητά τους αρχικά περιορίστηκε σε απλούστερα κυκλώματα.Η έλευση των CPLD στα μέσα της δεκαετίας του '80 επανάσταση σε αυτό το τοπίο, ανοίγοντας το δρόμο για σύνθετα σχέδια κυκλωμάτων.Έκτοτε, έχουν υφαντηθεί στον ιστό των βιομηχανιών όπως η δικτύωση, τα ηλεκτρονικά της αυτοκινητοβιομηχανίας, η μηχανική κατεργασία με CNC και τα αεροδιαστημικά συστήματα.Μπορείτε να θυμηθείτε για τον τρόπο με τον οποίο οι απλοποιημένες διαδικασίες CPLDs που κάποτε απαιτούσαν σχολαστική χειρωνακτική εργασία, σηματοδοτώντας ένα αξιοσημείωτο άλμα στην αποτελεσματικότητα.

Διακριτικές ιδιότητες των CPLD

Τα CPLDs διακρίνονται μέσω του προσαρμόσιμου προγραμματισμού τους, της εκτεταμένης ολοκλήρωσης, των δυνατοτήτων ανάπτυξης Swift και της ευρείας εφαρμογής, μαζί με το οικονομικό κόστος παραγωγής.Προσελκύουν όσους έχουν ελάχιστη εμπειρία υλικού, που χρησιμεύουν ως αξιόπιστα και ασφαλή προϊόντα που δεν απαιτούν εξαντλητικές δοκιμές.Ως απόδειξη της αντοχής τους σε σχέδια μεγάλης κλίμακας κυκλώματα, τα CPLD διαδραματίζουν βασικό ρόλο στην ανάπτυξη πρωτότυπου και σερβίρουν κάτω από 10.000 μονάδες, ενσωματώνοντας μια χρήσιμη ικανότητα για εσάς.Η έμπειρος με την οποία προσαρμόζονται οι CPLDs στις εξελισσόμενες απαιτήσεις του έργου συχνά τους κερδίζουν εκτίμηση, υπογραμμίζοντας την πραγματική τους ευελιξία σε δυναμικά περιβάλλοντα.

Μεθόδους εφαρμογής

Αυτά τα ολοκληρωμένα κυκλώματα σας επιτρέπουν να επεξεργαστείτε τις λογικές λειτουργίες προσαρμοσμένες στις ανάγκες τους χρησιμοποιώντας τόσο σχηματικά όσο και γλωσσικά περιγραφή υλικού σε πλατφόρμες ανάπτυξης.Για παράδειγμα, στο σχεδιασμό ενός μηχανισμού απάντησης, των σχημάτων και των περιγραφών υλικού προετοιμάζονται και καταρτίζονται σε έναν υπολογιστή.Χρησιμοποιώντας ένα καλώδιο λήψης, ο κώδικας μεταφέρεται στο CPLD για προγραμματισμό στο σύστημα, ο οποίος περιλαμβάνει δοκιμές, αντιμετώπιση προβλημάτων και ενίσχυση σχεδίων.Τα επιτυχημένα σχεδιασμένα σχέδια στη συνέχεια παράγονται μαζικά με την αναπαραγωγή των τσιπ CPLD.Σε έργα όπως τα συστήματα φωτός της κυκλοφορίας, η επανάληψη της διαδικασίας σχεδιασμού καθίσταται απαραίτητη, παρόμοια με την ανοικοδόμηση ενός σπιτιού για την αποκατάσταση της νεωτερικότητας του.Αυτή η επαναλαμβανόμενη μεθοδολογία συχνά θέτει τις βάσεις για την κυριαρχία, ενισχύοντας τόσο τις δεξιότητες όσο και την εμπιστοσύνη.

Κορυφαίες παραλλαγές

Καθ 'όλη τη διάρκεια των ετών, εταιρείες όπως η Altera, το Lattice και το Xilinx έχουν αποκαλύψει εξέχουσες γραμμές CPLD.Αξιοσημείωτα παραδείγματα περιλαμβάνουν το altera's EPM7128S, Πλέγμα LC4128V, και Xilinx's XC95108 .Αυτά τα μοντέλα έχουν βρει εξέχοντες ρόλους σε διάφορες παγκόσμιες εφαρμογές.Εκείνοι που είχαν το προνόμιο να συνεργαστούν με αυτά τα ξεχωριστά προϊόντα συχνά παρατηρούν τις λεπτές αλλά ισχυρές διαφορές που βελτιστοποιούν συγκεκριμένες λειτουργίες.Αυτό αντικατοπτρίζει μια διαδικασία επιλογής λεπτών επιλογών που επηρεάζεται από συγκεκριμένες απαιτήσεις έργου, όπου κάθε παραλλαγή κατέχει τη μοναδική του έκκληση.

Ταυτοποίηση και ταξινόμηση του FPGA και του CPLD

|

Αποψη |

CPLD |

FPGA |

|

Σχηματισμός λογικής συμπεριφοράς |

Σχηματίζουν λογική συμπεριφορά χρησιμοποιώντας τη δομή του όρου προϊόντος.

Παραδείγματα: σειρά Lattice ISPLSI, σειρά Xilinx XC9500, Altera Max7000s

Σειρά, Series Lattice Mach |

Δημιουργήστε λογική συμπεριφορά χρησιμοποιώντας μια μέθοδο αναζήτησης πίνακα.

Παραδείγματα: σειρά Xilinx Spartan, Altera Flex10K, σειρά Acex1K |

|

Επιτηδειότητα |

Κατάλληλο για αλγόριθμους και συνδυαστική λογική, έργα

Καλύτερα με περιορισμένους ενεργοποιητές και πλούσιους όρους προϊόντος |

Κατάλληλο για διαδοχική λογική, λειτουργεί καλύτερα

δομές πλούσιες σε ενεργοποιητές |

|

Καθυστέρηση χρονισμού |

Η συνεχής δομή καλωδίωσης παρέχει ομοιόμορφη και

προβλέψιμες καθυστερήσεις χρονισμού |

Η κατακερματισμένη δομή καλωδίωσης οδηγεί σε απρόβλεπτο χρονισμό

καθυστερήσεις |

|

Ευελιξία προγραμματισμού |

Τα σταθερά εσωτερικά κυκλώματα τροποποιούνται για προγραμματισμό.

Χρησιμοποιείται προγραμματισμός λογικού μπλοκ σε επίπεδο |

Η εσωτερική καλωδίωση τροποποιείται για προγραμματισμό.Λογική

Ο προγραμματισμός πύλης επιτρέπει μεγαλύτερη ευελιξία |

|

Ολοκλήρωση |

Χαμηλότερη ολοκλήρωση σε σύγκριση με το FPGA |

Υψηλότερη ενσωμάτωση με πιο σύνθετη δομή καλωδίωσης και

Λογική εφαρμογή |

|

Ευκολία χρήσης |

Ευκολότερη στη χρήση με προγραμματισμό μέσω E2Prom ή Fastflash.

Δεν απαιτείται εξωτερικό τσιπ μνήμης |

Απαιτεί εξωτερική μνήμη για την αποθήκευση προγραμματισμού

πληροφορίες, οδηγώντας σε πιο περίπλοκη χρήση |

|

Ταχύτητα και προβλεψιμότητα |

Ταχύτερη ταχύτητα και καλύτερη προβλεψιμότητα χρονισμού λόγω

συγκεντρωμένη διασύνδεση μεταξύ λογικών μπλοκ |

Βραδύτερη ταχύτητα και λιγότερο προβλέψιμο χρονισμό λόγω του

Προγραμματισμός σε επίπεδο πύλης και κατανεμημένη διασύνδεση |

|

Τεχνολογία προγραμματισμού |

Χρησιμοποιεί το E2PROM ή τον προγραμματισμό μνήμης flash.Δεδομένα προγραμματισμού

διατηρείται όταν το σύστημα είναι ενεργοποιημένο.Υποστηρίζει προγραμματισμό σε ένα

προγραμματιστής ή στο σύστημα |

Με βάση τον προγραμματισμό SRAM.Τα δεδομένα προγραμματισμού χάνουν όταν

Το σύστημα είναι ενεργοποιημένο και πρέπει να επαναφορτωθεί.Υποστηρίζει δυναμική

διαμόρφωση |

|

Εμπιστευτικότητα |

Προσφέρει καλύτερη εμπιστευτικότητα |

Παρέχει χαμηλότερη εμπιστευτικότητα |

|

Κατανάλωση ενέργειας |

Γενικά υψηλότερη κατανάλωση ενέργειας, ειδικά με

υψηλότερη ολοκλήρωση |

Χαμηλότερη κατανάλωση ενέργειας σε σύγκριση με το CPLD |

Γλώσσες προγραμματισμού του CPLD

Η ανάλυση του τρόπου με τον οποίο προγραμματίζονται πολύπλοκες προγραμματιζόμενες λογικές συσκευές (CPLDs) είναι ένας ακρογωνιαίος λίθος στη δημιουργία ευέλικτων λύσεων υλικού.Οι ιστορικές μέθοδοι για τον προγραμματισμό CPLD έχουν βασιστεί σε διαγράμματα σκάλας ή γλώσσες περιγραφής υλικού (HDLs), ενώ οι Verilog HDL και VHDL είναι κυρίαρχες επιλογές.Η επιλεγμένη γλώσσα μπορεί να διαμορφώσει τόσο τη στρατηγική σχεδιασμού όσο και την επιχειρησιακή αποτελεσματικότητα των υλοποιήσεων.

• Verilog HDL: Η Verilog HDL είναι αγαπημένη για την απλή σύνταξη και τις ισχυρές δυνατότητες προσομοίωσης, αντανακλώντας τις μεθοδολογίες που χρησιμοποιούνται στον σχεδιασμό της ψηφιακής λογικής.Η ενσωμάτωσή του με εργαλεία ηλεκτρονικού σχεδιασμού (EDA) σας επιτρέπει να διεξάγετε απρόσκοπτα σύνθεση και προσομοίωση.Η σύνταξη του Verilog παρατηρήθηκε για να μειώσει το φράγμα εισόδου για όσους έχουν υπόβαθρο προγραμματισμού, επιταχύνοντας το ταξίδι από το σχεδιασμό στην ανάπτυξη σε ένα ευρύ φάσμα βιομηχανικών τομέων.

• VHDL: Το VHDL παρέχει μια πιο περίπλοκη και εκφραστική επιλογή για τον προγραμματισμό HDL.Είναι συχνά η επιλογή για έργα που απαιτούν σχολαστική τεκμηρίωση και αυστηρό έλεγχο τύπου, χαρακτηριστικά που αποτιμώνται στην αεροδιαστημική και αμυντική βιομηχανία.Μπορείτε να σημειώσετε ότι παρά την πιθανή πολυπλοκότητα της VHDL σε μικρότερα έργα, η πειθαρχημένη δομή της υποστηρίζει τη δημιουργία εξαιρετικά αξιόπιστων σχεδίων, μια αναγκαιότητα σε περιβάλλοντα όπου κυριαρχεί η ασφάλεια.

Σχετικά με εμάς

ALLELCO LIMITED

Διαβάστε περισσότερα

Γρήγορη έρευνα

Στείλτε μια ερώτηση, θα απαντήσουμε αμέσως.

Transistors NMOS: Σχεδιασμός, Λειτουργία και Εφαρμογές

στο 2024/12/29

Το Fast Fourier Transform (FFT): Επαναστατική επεξεργασία ψηφιακού σήματος

στο 2024/12/29

Δημοφιλείς θέσεις

-

Σύνθετος σετ διδασκαλιών Ρύθμιση υπολογιστών: Πώς άλλαξαν τον υπολογισμό;

στο 8000/04/18 147764

-

Usb-c pinout και χαρακτηριστικά

στο 2000/04/18 111987

-

Χρήση Xilinx Unified Simulation Primitives: Ένας ολοκληρωμένος οδηγός για το σχεδιασμό και την προσομοίωση FPGA

στο 1600/04/18 111351

-

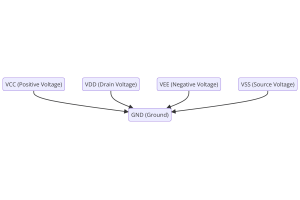

Τάσεις τροφοδοσίας στα ηλεκτρονικά: Έννοια των VCC, VDD, VEE, VSS και GND

στο 0400/04/18 83751

-

Οδηγός σύνδεσης RJ45: Pinout, καλωδίωση, τύποι καλωδίων και χρήσεις

στο 1970/01/1 79542

-

Ο τελικός οδηγός για τους χρωματικούς κωδικούς σε σύγχρονα ηλεκτρικά συστήματα

Ο τρόπος με τον οποίο τα ηλεκτρικά μας συστήματα χρησιμοποιούν τα χρώματα δεν είναι μόνο για εμφάνιση.Κάθε χρώμα καλωδίου υποδεικνύει τώρα μια συγκεκριμένη λειτουργία, καθιστώντας ευκολότερο τον εν...στο 1970/01/1 66949

-

Οδηγός βαλβίδας καθαρισμού: Λειτουργία, συμπτώματα, δοκιμές και αντικατάσταση για τη βέλτιστη απόδοση του κινητήρα

Η βαλβίδα εκκαθάρισης είναι ένα βασικό μέρος του συστήματος ενός αυτοκινήτου που βοηθά στη διατήρηση του αέρα καθαρό με τη διαχείριση των ατμών καυσίμων προτού μπορέσουν να ξεφύγουν στην ατμόσφαιρα...στο 1970/01/1 63091

-

Παράγοντας ποιότητας (Q): Εξισώσεις και εφαρμογές

Ο παράγοντας ποιότητας ή το «Q» είναι σημαντικός όταν ελέγχετε πόσο καλά οι επαγωγείς και οι συντονιστές λειτουργούν σε ηλεκτρονικά συστήματα που χρησιμοποιούν ραδιοσυχνότητες (RF).Το 'Q' μετράει π...στο 1970/01/1 63028

-

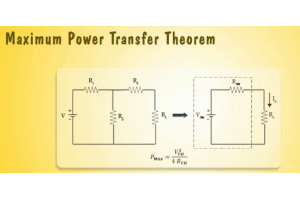

Επιτυχία αιχμής από την απόδοση με το θεώρημα μέγιστης ισχύος

Το μέγιστο θεώρημα μεταφοράς ισχύος εξηγεί πώς η ενέργεια από μια πηγή, όπως μια μπαταρία ή γεννήτρια, ρέει σε ένα συνδεδεμένο φορτίο.Δείχνει την ακριβή κατάσταση όπου το φορτίο λαμβάνει την μεγαλύ...στο 1970/01/1 54092

-

Προδιαγραφές μπαταρίας A23 και συμβατότητα

Η μπαταρία A23 είναι μια μικρή μπαταρία σε σχήμα κυλίνδρου με υψηλή τάση.Ονομάζεται επίσης 23Α, 23AE ή MN21, τρέχει σε 12 βολτ και πολύ υψηλότερα από τις μπαταρίες ΑΑ ή ΑΑΑ.Ο ειδικός σχεδι...στο 1970/01/1 52172